Avalon-st tx interface, Avalon-st tx interface -16 – Altera Arria 10 Avalon-ST User Manual

Page 82

The smallest PCIe packet, such as a 3-dword memory read, uses 96 bits of the 256-bits bus and achieve the

following throughput:

96/256*8 = 3 GBytes/sec

If you enable mMultiple Packets Per Cycle, when a TLP ends in the upper 128 bits of the Avalon-ST bus,

a new TLP can start in the lower 128 bits Consequently, the bandwidth of small packets doubles:

96*2/256*8 = 3 GBytes/sec

This mode adds complexity to the Application Layer user decode logic. However, it could result in higher

throughput.

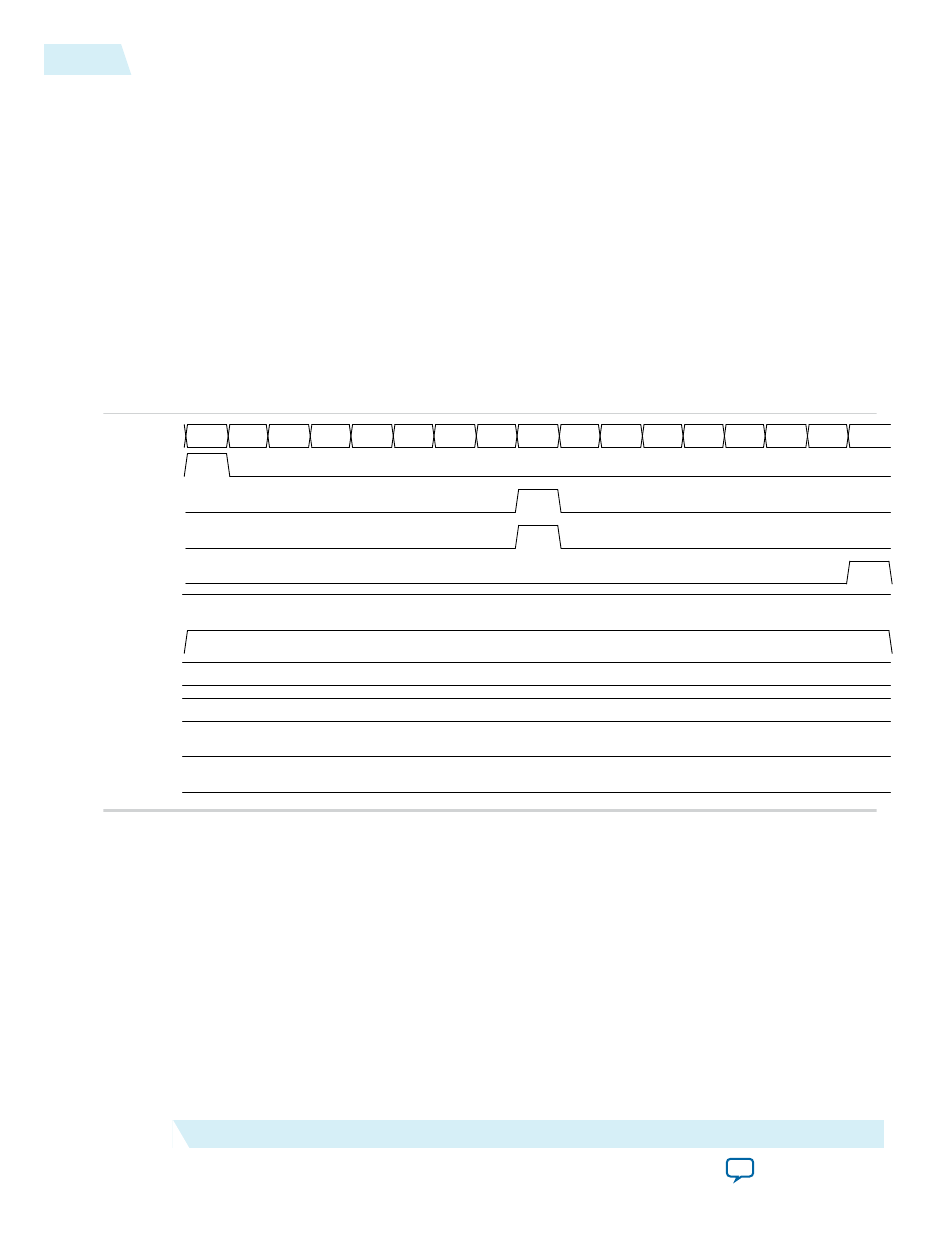

Figure 6-18: 256-Bit Avalon-ST RX Interface with Multiple Packets Per Cycle

The following figure illustrates this mode for a 256-bit Avalon-ST RX interface. In this figure

rx_st_eop[0]

and

rx_st_sop[1]

are asserted in the same cycle.

rx_st_sop[0]

rx_st_eop[0]

rx_st_sop[1]

rx_st_eop[1]

rx_st_data[255:0]

rx_st_bar[7:0]

rx_st_empty[1:0]

rx_st_err

rx_st_mask

rx_st_ready

rx_st_valid

.. 12...

12... 12...

12... 12...

12... 12...

12... 00...

12... 12...

12... 12...

12... 12...

12... 003458

00

Avalon-ST TX Interface

The following table describes the signals that comprise the Avalon-ST TX Datapath. The TX data signal

can be 64, 128, or 256 bits.

6-16

Avalon-ST TX Interface

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions