Altera Arria 10 Avalon-ST User Manual

Page 152

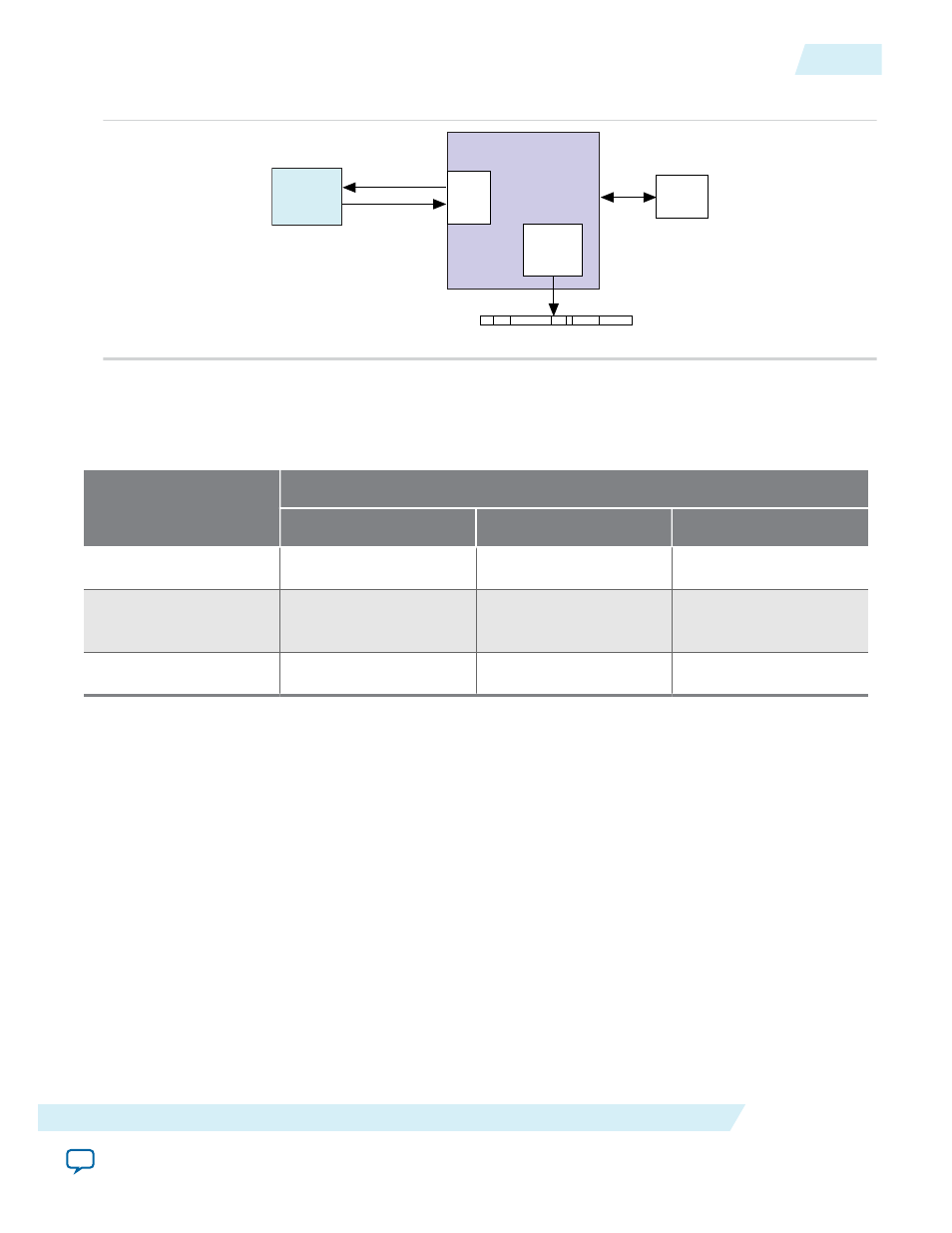

Figure 9-3: MSI Request Example

Endpoint

8 Requested

2 Allocated

Root Complex

CPU

Interrupt Register

Root

Port

Interrupt

Block

The following table describes three example implementations. The first example allocates all 32 MSI

messages. The second and third examples only allocate 4 interrupts.

Table 9-1: MSI Messages Requested, Allocated, and Mapped

MSI

Allocated

32

4

4

System Error

31

3

3

Hot Plug and Power

Management Event

30

2

3

Application Layer

29:0

1:0

2:0

MSI interrupts generated for Hot Plug, Power Management Events, and System Errors always use Traffic

Class 0. MSI interrupts generated by the Application Layer can use any Traffic Class. For example, a DMA

that generates an MSI at the end of a transmission can use the same traffic control as was used to transfer

data.

The following figure illustrates the interactions among MSI interrupt signals for the Root Port. The

minimum latency possible between

app_msi_req

and

app_msi_ack

is one clock cycle. In this timing

diagram

app_msi_req

can extend beyond

app_msi_ack

before deasserting. However,

app_msi_req

must

be deasserted before or within the same clock as

app_msi_ack

is deasserted to avoid inferring a new

interrupt.

UG-01145_avst

2015.05.04

MSI Interrupts

9-3

Interrupts

Altera Corporation