Compiling the design in the qsys design flow, Compiling the design in the qsys design flow -5 – Altera Arria 10 Avalon-ST User Manual

Page 24

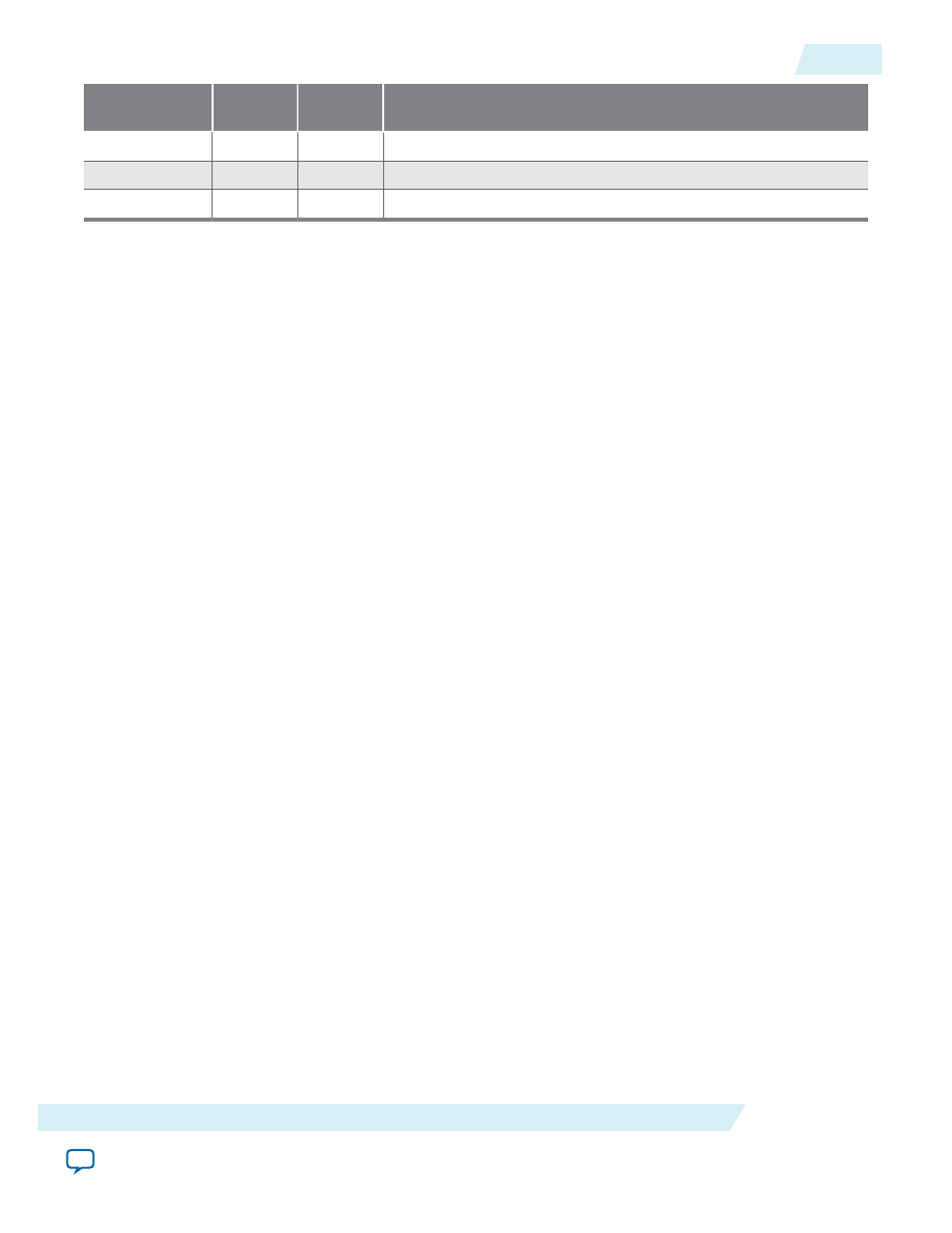

Time

TLP Type

Payload

(Bytes)

TLP Header

18021 RX

CfgRd0

0004

04000001_0000010F_0108002C

18053 RX

CfgRd0

0004

04000001_0000030F_0108003C

18085 RX

MRd

0000

00000000_00000000_0108000C

Understanding Physical Placement of the PCIe IP Core

For more information about physical placement of the PCIe blocks, refer to the links below. Contact your

Altera sales representative for detailed information about channel and PLL usage.

Related Information

•

Channel Placement and fPLL Usage for the Gen1 and Gen2 Data Rates

on page 5-5

•

Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate

on page 5-7

Adding Virtual Pin Assignment to the Quartus II Settings File (.qsf)

To compile successfully you must add a virtual pin assignment statement for the PIPE interface to

your

.qsf

file. The PIPE interface is useful for debugging, but is not a top-level interface of the IP core.

1. Browse to the synthesis directory that includes the

.qsf

for your project,

<project_dir>/ep_g1x8/

2. Open

ep_g1x8.qsf

.

3. Add the following assignment statement:

set_instance_assignment -name VIRTUAL_PIN ON -to hip_pipe_*

4. Save the

.qsf

file.

Compiling the Design in the Qsys Design Flow

To compile the Qsys design example in the Quartus II software, you must create a Quartus II project and

add your Qsys files to that project.

1. Before compiling, you can optionally turn on two parameters in the testbench. The first parameter

specifies pin assignments that match those for the Altera Development Kit board I/Os. The second

parameter enables the Compliance Base Board (CBB) logic on the development board. In the Gen1 x8

example design, complete the following steps if you want to enable these parameters:

a. Right-click the APPS component and select Edit.

b. Turn on Enable FPGA Dev kit board I/Os.

c. Turn on Enable FPGA Dev kit board CBB logic.

d. Click Finish.

e. On the Generate menu, select Generate Testbench System and then click Generate.

f. On the Generate menu, select Generate HDL and then click Generate. (You can use the same

parameters that are specified in Generating the Testbench earlier in this chapter).

2. In the Quartus II software, click the New Project Wizard icon.

3. Click Next in the New Project Wizard: Introduction (The introduction does not appear if you

previously turned it off.)

4. On the Directory, Name, Top-Level Entity page, enter the following information:

UG-01145_avst

2015.05.04

Understanding Physical Placement of the PCIe IP Core

2-5

Getting Started with the Arria 10 Hard IP for PCI Express

Altera Corporation