Altera Arria 10 Avalon-ST User Manual

Page 20

Getting Started with the Arria 10 Hard IP for PCI

Express

2

2015.05.04

UG-01145_avst

This section provides instructions to help you quickly customize, simulate, and compile the Arria 10 Hard

IP for PCI Express IP Core. When you install the Quartus II software you also install the IP Library. This

installation includes design examples for Hard IP for PCI Express under the

<install_dir>/ip/altera/altera_

pcie/

directory.

After you install the Quartus II software, you can copy the design examples from the

<install_dir>/ip/altera/

altera_pcie/altera_pcie_a10_ed/example_design/a10

directory. This walkthrough uses the Gen1 ×8 Endpoint,

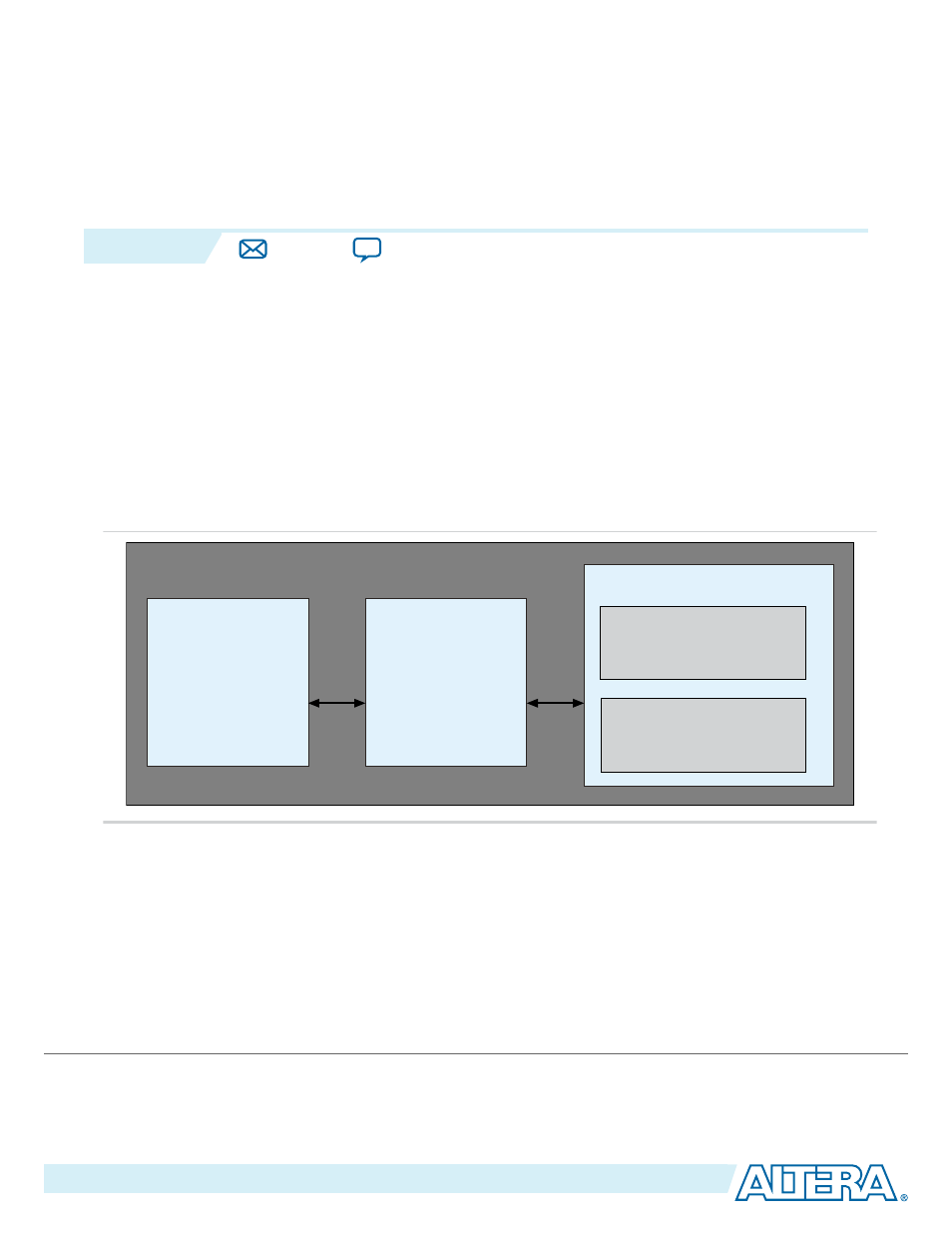

ep_g1x8.qsys. The following figure illustrates the top-level modules of the testbench in which the DUT, a

Gen1 Endpoint, connects to a chaining DMA engine, labeled APPS in the following figure, and a Root

Port model. The simulation can use the parallel PHY Interface for PCI Express (PIPE) or serial interface.

Figure 2-1: Testbench for an Endpoint

APPS

altpcied_<dev>_hwtcl.v

Hard IP for PCI Express Testbench for Endpoints

Avalon-ST TX

Avalon-ST RX

reset

status

Avalon-ST TX

Avalon-ST RX

reset

status

DUT

<instance_name>_altera_pcie

_a10_hip_<version>

_<generated_string>.v

Root Port Model

altpcie_tbed_<dev>_hwtcl.v

PIPE or

Serial

Interface

Root Port BFM

altpcietb_bfm_rpvar_64b_x8_pipen1b

Root Port Driver and Monitor

altpcietb_bfm_vc_intf

Note: The Quartus II software automatically creates a simulation log file,

altpcie_monitor_<dev>_dlhip_tlp_

file_log.log

, in your simulation directory. Refer to Understanding Simulation Log File Generation for

details.

Altera provides example designs to help you get started with the Arria 10 Hard IP for PCI Express IP

Core. You can use example designs as a starting point for your own design. The example designs include

scripts to compile and simulate the Arria 10 Hard IP for PCI Express IP Core. This example design

provides a simple method to perform basic testing of the Application Layer logic that interfaces to the

Hard IP for PCI Express.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134