Altera Arria 10 Avalon-ST User Manual

Page 71

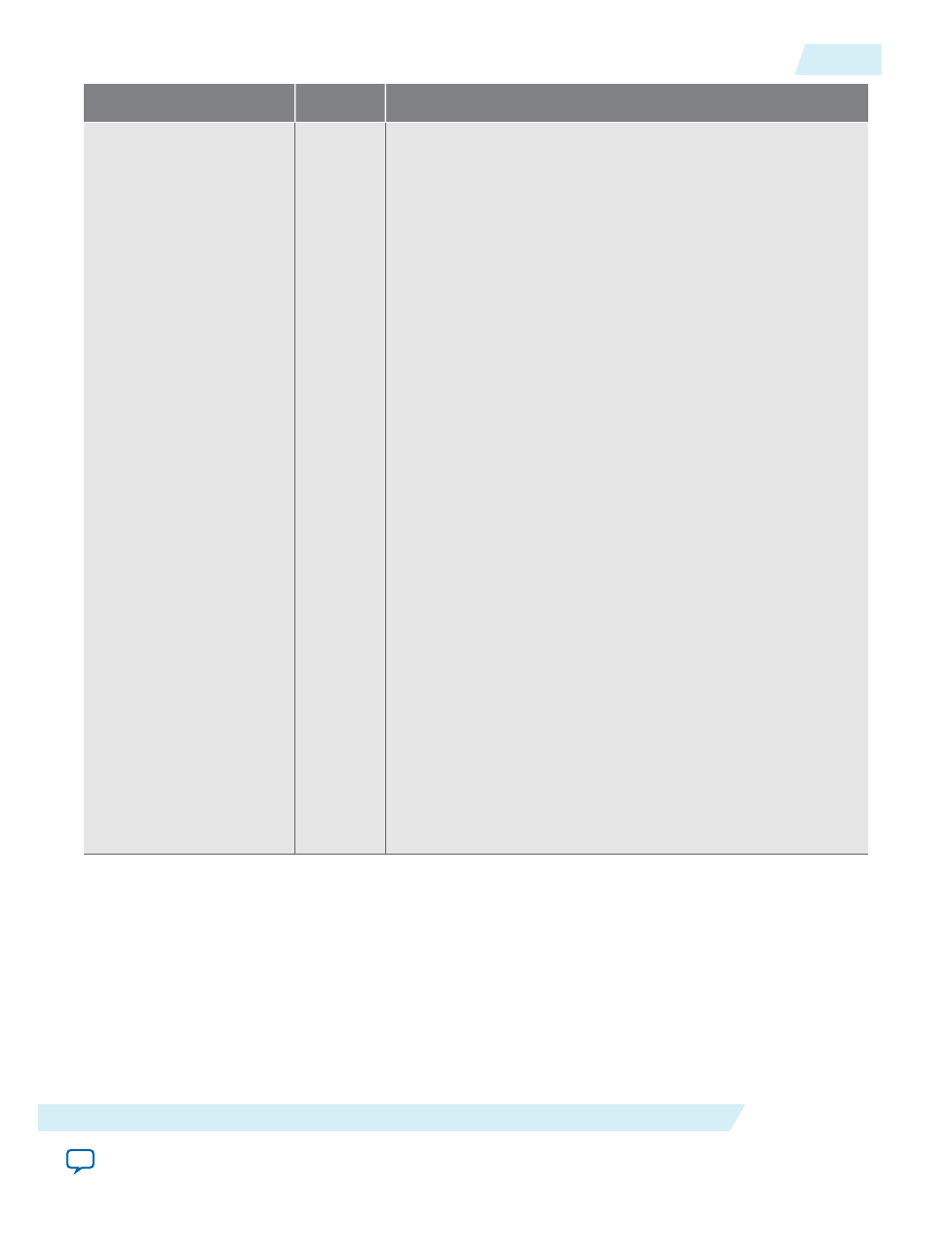

Signal

Direction

Description

rx_st_bar[7:0]

Output

The decoded BAR bits for the TLP. Valid for

MRd

,

MWr

,

IOWR

, and

IORD

TLPs. Ignored for the completion or message TLPs. Valid

during the cycle in which

rx_st_sop

is asserted.

Refer to 64-Bit Avalon-ST rx_st_data<n> Cycle Definitions for 4-

Dword Header TLPs with Non-Qword Addresses and 128-Bit

Avalon-ST rx_st_data<n> Cycle Definition for 3-Dword Header

TLPs with Qword Aligned Addresses for the timing of this signal

for 64- and 128-bit data, respectively.

The following encodings are defined for Endpoints:

• Bit 0: BAR 0

• Bit 1: BAR 1

• Bit 2: Bar 2

• Bit 3: Bar 3

• Bit 4: Bar 4

• Bit 5: Bar 5

• Bit 6: Expansion ROM

• Bit 7: Reserved

The following encodings are defined for Root Ports:

• Bit 0: BAR 0

• Bit 1: BAR 1

• Bit 2: Primary Bus number

• Bit 3: Secondary Bus number

• Bit 4: Secondary Bus number to Subordinate Bus number

window

• Bit 5: I/O window

• Bit 6: Non-Prefetchable window

• Bit 7: Prefetchable window

For multiple packets per cycle, this signal is undefined. If you

turn on Enable multiple packets per cycle, do not use this signal

to identify the address BAR hit.

UG-01145_avst

2015.05.04

Avalon‑ST RX Component Specific Signals

6-5

Interfaces and Signal Descriptions

Altera Corporation