Altera ALTDLL User Manual

Page 25

Chapter 3: Parameter Settings

3–7

ALTDQ_DQS Parameter Editor

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

The Advanced Options page allows you to configure the parameters in the following

pages:

■

DQS IN

■

DQS OUT/OE

■

DQ IN

■

DQ OUT/OE

■

Half-rate

■

OCT Path

■

DQSn I/O

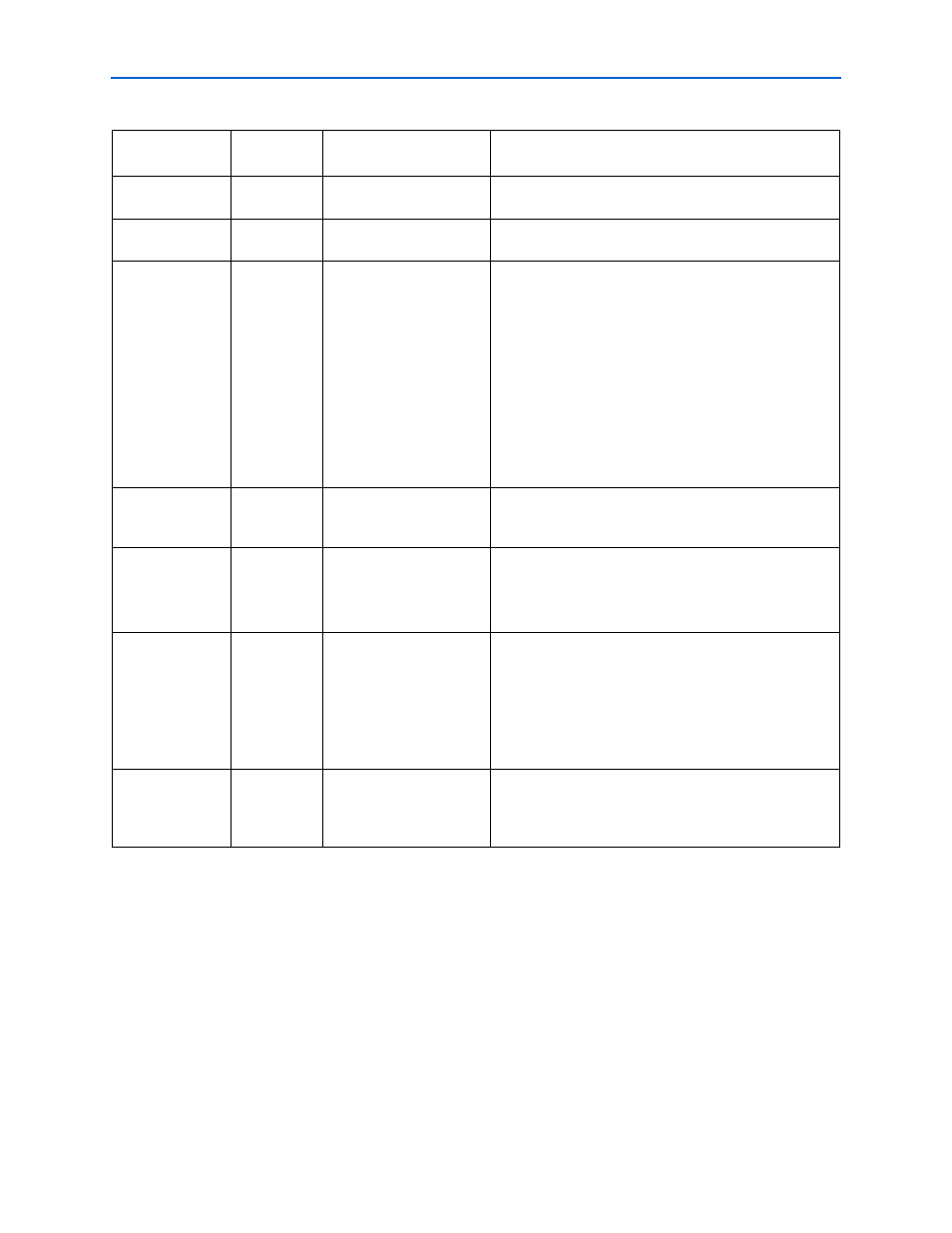

Number of input

DQ

0–48

NUMBER_OF_

INPUT_DQ

Specifies the number of input DQ ports used in the

ALTDQ_DQS instance.

Number of output

DQ

0–48

NUMBER_OF_

OUTPUT_DQ

Specifies the number of output DQ ports used in the

ALTDQ_DQS instance.

Number of stages

in

dqs_delay_chain

1, 2, 3, and 4

DQS_DELAY_CHAIN_

PHASE_SETTING

Specifies the stages of

DQS_DELAY_CHAIN

. The

number of stages depends on the intended phase shift

that you want to clock for <IO>

_DDIO_IN

block in the

DQ input path. The bigger the value you specify, the longer

the delay.

The coarse phase shift depends on this option. For

example, in Stratix IV devices, if you set the frequency

mode to 1, you will get a phase shift of 20°, 60°, 90°, or

120°. If you set Number of stages in dqs_delay_chain

value to 2, you will get 60° phase shift and if you set the

Number of stages in dqs_delay_chain value to 1, you will

get 30° phase shift.

DQS input

frequency

—

DQS_INPUT_

FREQUENCY

Specifies the input frequency of the DQS strobe in MHz.

The input frequency must match the DLL (ALTDLL) input

frequency.

Use half rate

components

—

USE_HALF_RATE

Instantiates the half-rate blocks in the ALTDQ_DQS

instance. This parameter is used only when the external

memory interface requires half-rate mode.

Not supported in Arria II GX devices.

Use dynamic OCT

path

—

USE_DYNAMIC_OCT

Instantiates the dynamic OCT blocks in the ALTDQ_DQS

instance. This parameter enables access to dynamic OCT

paths on both DQ and DQS paths. The dynamic OCT

features enable parallel termination (R

t

) during reads from

the external memory and disable R

t

during writes to the

external memory.

Not supported in Arria II GX devices.

Add memory

interface specific

fitter grouping

assignments

—

ADD_MEM_FITTER_

GROUP_ASSIGNMENTS

Enables the Quartus II Fitter to automatically assign the

memory interface I/O ports to the memory interface I/O

pins on the FPGA.

Table 3–3. Options on Parameter Settings Page (Part 2 of 2)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description