Altera ALTDLL User Manual

Page 26

3–8

Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

■

Reset/Config Ports

describes the options available on the DQS IN page. This page allows you

to configure the DQS input path. For more information about the DQS input path,

refer to

.

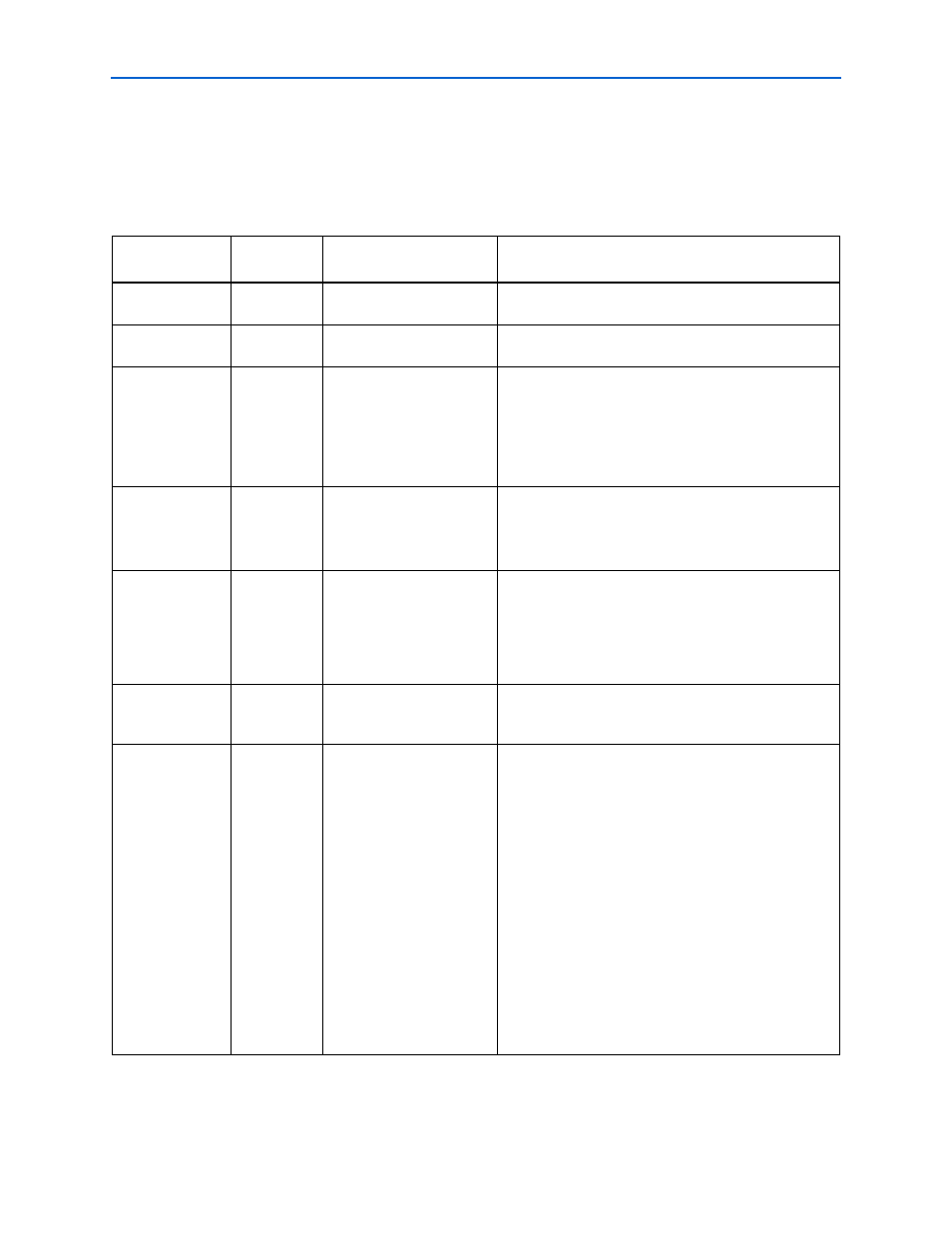

Table 3–4. Options on DQS IN Page (Part 1 of 3)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

Enable DQS Input

Path

—

USE_DQS_INPUT_PATH

Instantiates the DQS input path.

Enable DQS Input

Path

—

USE_DQS_INPUT_PATH

Instantiates the DQS input path.

Delay chain

usage:

Enable dynamic

delay chain

—

USE_DQS_INPUT_

DELAY_CHAIN

Enables <IO>

_INPUT_DELAY_CHAIN

(D1) on the

DQS input path. If you turn on this parameter,

DQS_DELAY_CHAIN

block in the path is disabled. D1

is a run-time adjustable delay chain.

To configure delay chains dynamically, refer to

.

Delay chain

usage:

Enable

dqs_delay_chain

—

USE_DQS_DELAY_

CHAIN

Enables

DQS_DELAY_CHAIN

block. The DQS delay

chain is a DLL-controlled delay chain used to phase shift

the DQS read clock.

Enable DQS

busout delay

chain

—

USE_DQSBUSOUT_

DELAY_CHAIN

Enables

DQSBUSOUT_DELAY_CHAIN

(Da). This

busout delay chain fine-tunes the outputs of

DQS_DELAY_CHAIN

block so that the DQS strobe

timing matches the DQS enable signal. The DQS strobe

has 15 steppable delays, with each step having 50 ps of

delay. Da is a run-time adjustable delay chain.

Enable DQS

enable block

—

USE_DQS_ENABLE

Enables

DQS_ENABLE

block. This block grounds the

DQS input strobe when the strobe goes to high

impedance state (Z) after a DDR read postamble.

Enable DQS

enable control

block

—

USE_DQS_ENABLE_

CTRL

Enables

DQS_ENABLE_CTRL

block that controls a

DQS enable circuitry.

You must determine an efficient working

resync_postamble_clk

clock phase which clocks

this block to ensure smooth data transfer. The

ALTDQ_DQS megafunction cannot determine the phase

for the data transfer.

Use round trip delay (RTD) analysis or create a custom

data training circuitry to write and read back a training

pattern to and from the memory device and then

dynamically adjust the PLL’s resyncronization clock

phase to find an efficient working phase.

Even though this block controls the DQS enable signal,

the megafunction does not consider the necessary

timing for this signal. Refer to the external memory

interface requirements for the necessary timing.