Altdq_dqs megafunction, Altdq_dqs megafunction –4, Table 4–2 – Altera ALTDLL User Manual

Page 40: Altdq_dqs

Chapter 4: Functional Description

4–4

ALTDQ_DQS Megafunction

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

The names

DLL_OFFSET_CTRL_A

and

DLL_OFFSET_CTRL_B

are logical and do not

denote the placement of the actual phase-offset blocks. With location assignments,

you can assign these blocks to the top, bottom, or side of the FPGA, depending on

which DLL your design uses. If location assignments are not used, the Quartus II

Fitter places these blocks on the top, bottom, or side of the FPGA device.

The DLL and DLL offset blocks in the DQS phase shift circuitry generate the control

signals to shift the DQS delay chain delays to center align the DQS strobe with the

incoming DQ data at the IOE registers. This is common when reading from external

memory interfaces. For more information about the DLL offset control blocks in the

DQS phase shift circuitry, refer to the DQS Phase Shift Circuitry section in the

respective device handbooks.

For more information about the ALTDLL megafunction ports, refer to

Megafunction Ports” on page 4–31

.

ALTDQ_DQS Megafunction

This section describes the DQ/DQS datapaths and the associated blocks of the

ALTDQ_DQS megafunction. The figures in the subsequent sections show the

megafunction blocks used to construct the datapath and their connections of the

top-level ports with the blocks that configure the paths. You must set the appropriate

parameters using the parameter editor to enable the blocks and the desired

configurations in the paths.

list the common blocks that are used in the DQ/DQS input and output

paths:

1

The value for <IO> depends on your selection in the parameter editor. The possible

values are

BIDIR_DQ

and

INPUT_DQ

.

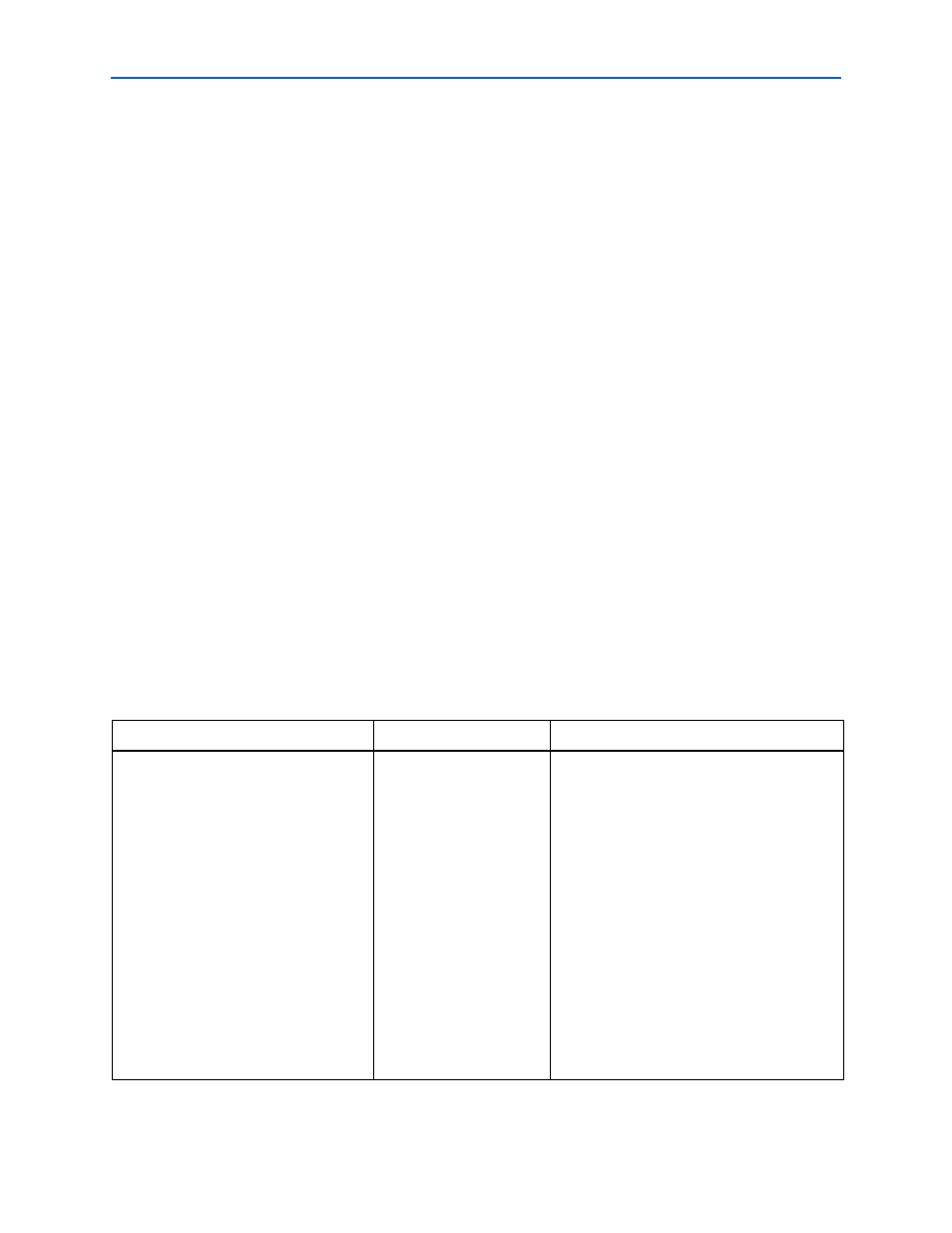

Table 4–2. Common Blocks in the DQ/DQS Input and Output Paths (Part 1 of 2)

Block Name

Description

DQS_DELAY_CHAIN

DQS_INPUT_DELAY_CHAIN

(D1)

DQSBUSOUT_DELAY_CHAIN

(Da)

DQS_ENABLE_DELAY_CHAIN

(Db)

<IO>

_INPUT_DELAY_CHAIN

(D1)

<IO>

_OUTPUT_DELAY_CHAIN1

(D5)

<IO>

_OUTPUT_DELAY_CHAIN2

(D6)

DQS_OUTPUT_DELAY_CHAIN1

(D5)

DQS_OUTPUT_DELAY_CHAIN2

(D6)

<IO>

_OE_DELAY_CHAIN1

(D5)

<IO>

_OE_DELAY_CHAIN2

(D6)

DQS_OE_DELAY_CHAIN1

(D5)

DQS_OE_DELAY_CHAIN2

(D6)

<IO>

_OCT_DELAY_CHAIN1

(D5 OCT)

<IO>

_OCT_DELAY_CHAIN2

(D6 OCT)

Delay Chains

Represents the delay chains used to delay

signals.

For more information about the DQS delay chain

block, refer to the DQS Delay Chain section of

the respective device handbooks.

For more information about the delay chain

types and settings, refer to