Altdq_dqs megafunction ports, Dqs input path megafunction ports, Altdq_dqs megafunction ports –33 – Altera ALTDLL User Manual

Page 69: Dqs input path megafunction ports –33

4–33

Chapter 4: Functional Description

ALTDQ_DQS Megafunction Ports

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

ALTDQ_DQS Megafunction Ports

to

describes the ports of the ALTDQ_DQS megafunction that

you can use to configure the DQS input path, DQS output path, DQS OE path,

DQ/DQS OCT path, DQ input path, DQ output path, DQ OE path, DQSN IO path,

and DQS_CONFIG/IO_CONFIG path.

DQS Input Path Megafunction Ports

summarizes all the ports on the megafunction to configure the DQS input

path.

n

b

= number of bidirectional DQ

n

o

= number of output DQ

n

i

= number of input DQ

n

c

= number of clock divider

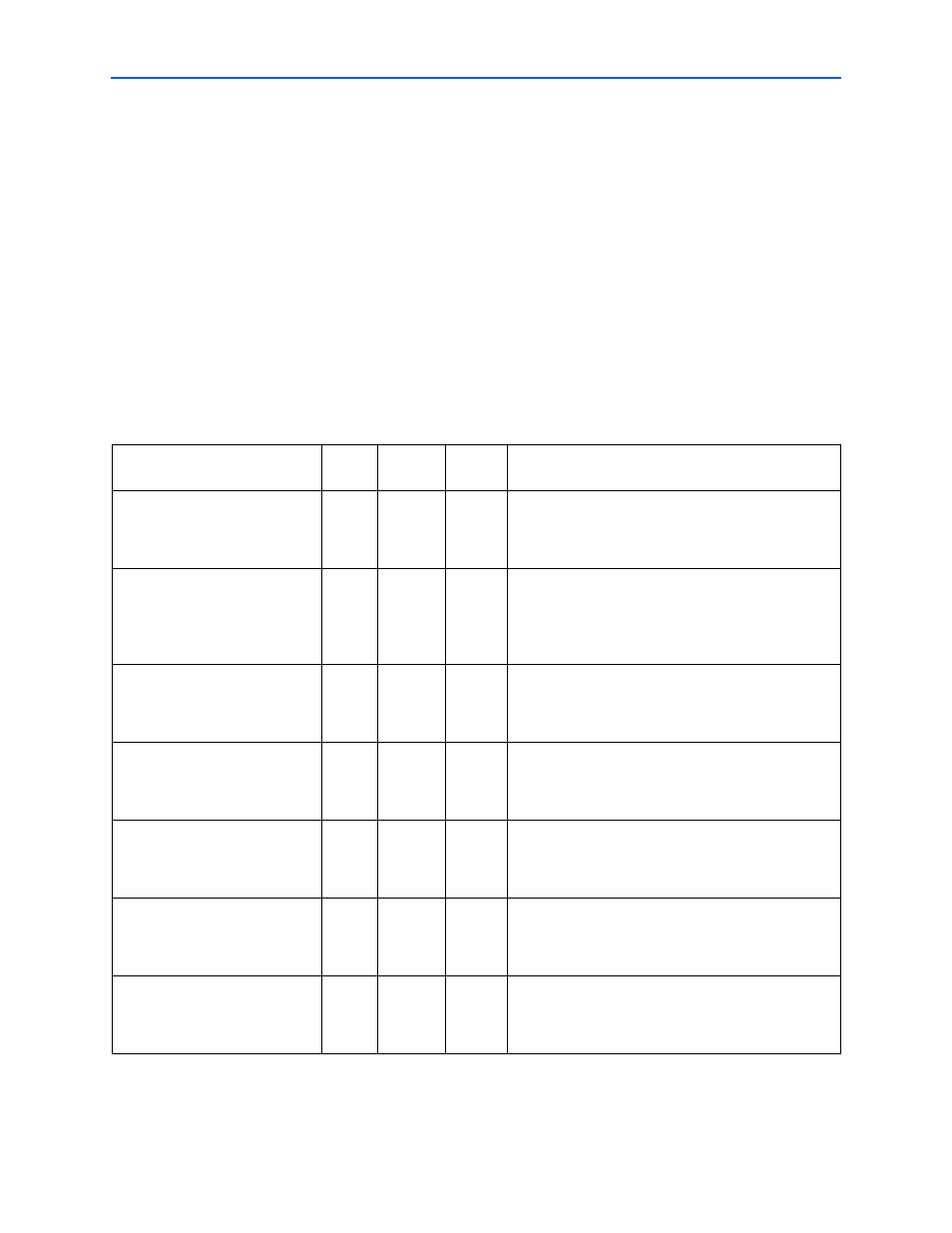

Table 4–11. Megafunction Ports to Configure DQS Input Path

(Part 1 of 2)

Port Name

Type

Optional/

Required

Default

Description

core_delayctrlin[5..0]

Input

Optional

GND

This port receives the Gray-coded delay chain setting

for the DQS read path from the FPGA core. This port

does not need to match the polarity of its source and

can be inverted.

dll_delayctrlin[5..0]

Input

Optional

GND

This port receives the Gray-coded delay chain setting

for the DQS read path from the

ALTDLL:delayctrlout[5..0]

port. This port

must match the polarity of its source and cannot be

inverted.

dqs_bus_out

Output

Optional

—

This port receives the possibly delayed DQS output

signal from the

DQS_ENABLE:dqsbusout

,

DQSBUSOUT_DELAY_CHAIN:dataout

, or

DQS_DELAY_CHAIN:dqsbusout

port.

dqs_enable_ctrl_clk

Input

Optional

V

CC

This port is connected to the

DQS_ENABLE_CTRL:clk

port that is used to

capture the

DQS_ENABLE_CTRL:dqsenablein

signal.

dqs_enable_ctrl_hr_

datainhi

Input

Optional

GND

This port is connected to the

DQS_ENABLE_CTRL_HR_DDIO_OUT:datainhi

port. This port receives the half-rate data for the rising

edge of the

IO_CLOCK_DIVIDER:clkout

signal.

dqs_enable_ctrl_hr_

datainlo

Input

Optional

GND

This port is connected to the

DQS_ENABLE_CTRL_HR_DDIO_OUT

:

datainlo

port. This port receives the half-rate data for the falling

edge of the

IO_CLOCK_DIVIDER:clkout

signal.

dqs_enable_ctrl_in

Input

Optional

V

CC

This active-high port is connected to the

DQS_ENABLE_CTRL:dqsenablein

port that is

used to enable or disable the

DQS_ENABLE_CTRL:dqsenableout

port.