Er to, Figure 4–25 on, Figure 4–25 – Altera ALTDLL User Manual

Page 99

4

–63

Ch

apt

er

4:

F

u

n

c

tiona

l

De

sc

rip

tio

n

De

sign Ex

ample: Implem

enting Ha

lf-

R

ate

DDR

2

Inter

face in

Stra

tix

III

AL

TD

LL

an

d

©

February 2012

Al

tera Cor

por

atio

n

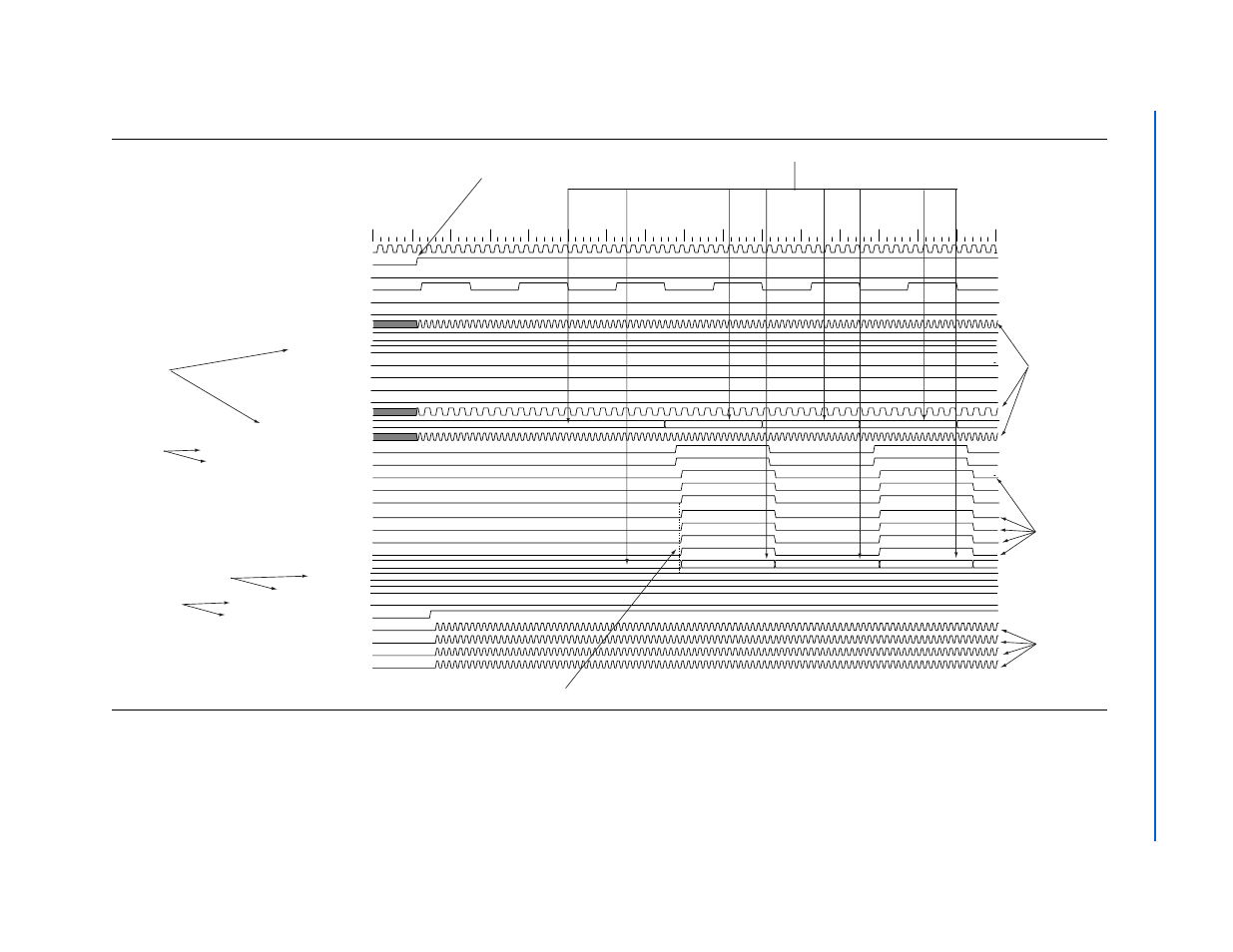

Figure 4–25. Data Transfer From the FPGA Core to the Bidirectional DQ Pin with No Delay Chains Activated

bidir_dq_0_output_delay_chain1_inst.dataout

bidir_dq_0_output_delay_chain2_inst.dataout

bidir_dq_io[7:0]

dqs_hr_oe_in[1:0]

dqs_hr_output_data_in[3:0]

dqs_output_hr_ddio_out_low_inst.dataout

dqs_output_hr_ddio_out_high_inst.dataout

dqs_output_delay_chain1_inst.dataout

dqs_output_delay_chain2_inst.dataout

dqs_output_ddio_out_inst.dataout

dqs_io

00

FF

00

FF

inclk0

locked

areset

config_clk

config_datain

config_update

c2

bidir_dq_io_config_ena[7:0]

bidir_dq_hr_oe_in[15:0]

bidir_dq_0_oe_ddio_oe_inst.dataout

bidir_dq_0_oe_hr_ddio_out_inst.dataout

bidir_dq_0_oe_delay_chain1_inst.dataout

bidir_dq_0_oe_delay_chain2_inst.dataout

c3

bidir_dq_hr_output_data_in[31:0]

c1

bidir_dq_0_output_hr_ddio_out_high_inst.dataout

bidir_dq_0_output_hr_ddio_out_low_inst.dataout

bidir_dq_0_output_ddio_out_inst.dataout

output_dq_0_output_delay_chain1_inst.dataout

output_dq_0_output_delay_chain2_inst.dataout

00

00000000

FFFFFFFF

00000000

FFFFFFFF

0ns

20ns

40ns

60ns

80ns

100ns

120ns

140ns

160ns

180ns

200ns

220ns

240ns

260ns

280ns

300ns

[1]

bidir_dq_0_output_delay_chain1_inst.datain

bidir_dq_0_output_delay_chain2_inst.datain

[2]

[3]

[5]

[7]

[8, 9, 10]

[12]

[13, 14, 15]

[16]

[17,18]