Altera ALTDLL User Manual

Page 27

Chapter 3: Parameter Settings

3–9

ALTDQ_DQS Parameter Editor

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

Enable DQS

enable block

delay chain

—

—

Enables

DQS_ENABLE_DELAY_CHAIN

(Db) that

fine-tunes the outputs of

DQS_ENABLE_CTRL

block

so that the DQS enable signal timing matches the DQS

strobe. Db is a run-time adjustable delay chain.

Advanced Delay

Chain Options

Set dynamically

using

configuration

registers

—

USE_DQS_DELAY_

CHAIN_PHASECTRLIN

Determines the

phasectrlin

input for the phase

setting. If you turn on this option, it dynamically chooses

the phase applied to the

dqsbusout

output during the

FPGA run time. If you turn off this option, the phase

setting is determined by the Number of stages in

dqs_delay_chain option in the Parameter Settings

page. This delay chain fine-tunes the DQS strobe signal.

Advanced Delay

Chain Options

DQS delay chain

delayctrlin port

source

DLL or Core

DQS_DELAY_CHAIN_

DELAYCTRLIN_SOURCE

Determines whether you want the

delayctrlin

port

to be controlled by DLL (outputs) or from the Core

(FPGA).

If you select DLL, the

dll_delayctrlin[5..0]

port is connected to the

dll_delayctrlout[5..0]

port of the DLL. The

DLL option adjusts the delay setting in

DQS_DELAY_CHAIN

block across pressure, volume,

and temperature (PVT). Altera recommends that you

always select DLL to optimize the read capture at the DQ

input register. If you select Core, the

core_delayctrlin

port is fed by the core.

Advanced Delay

Chain Options

DQS Delay Buffer

Mode

Low or High

DELAY_BUFFER_MODE

Specifies whether the variable delay buffers in the

DQS_DELAY_CHAIN

work in low-frequency or

high-frequency mode. The frequency mode must match

the frequency mode you select for the DQS Delay Buffer

Mode parameter on the Parameter Settings page in the

ALTDLL parameter editor.

Advanced Delay

Chain Options

DQS Phase Shift

0–36,000

DQS_PHASE_SHIFT

Specifies the phase shift between the delayed DQS signal

and the input DQS signal in units of hundreds of degrees,

for example, a 90° phase shift is represented as 9,000.

Use this parameter for static timing analysis only

because timing analysis cannot determine the phase

shift through the

delayctrlin[5..0]

,

phasectrlin[2..0]

, and

offsetctrlin[5..0]

ports on the megafunction

the way a simulation can. This is an optional field and

defaults to 0.

Advanced Delay

Chain Options

Enable DQS

offset control

—

DQS_OFFSETCTRL_

ENABLE

Enables offset values to be added to

DQS_DELAY_CHAIN

block. If you turn on this option,

make sure that the ALTDLL instance is set to use the DLL

offset control blocks. This option connects the outputs

from the DLL offset control blocks to the DQS delay

chain block. This parameter is optional and turned off by

default.

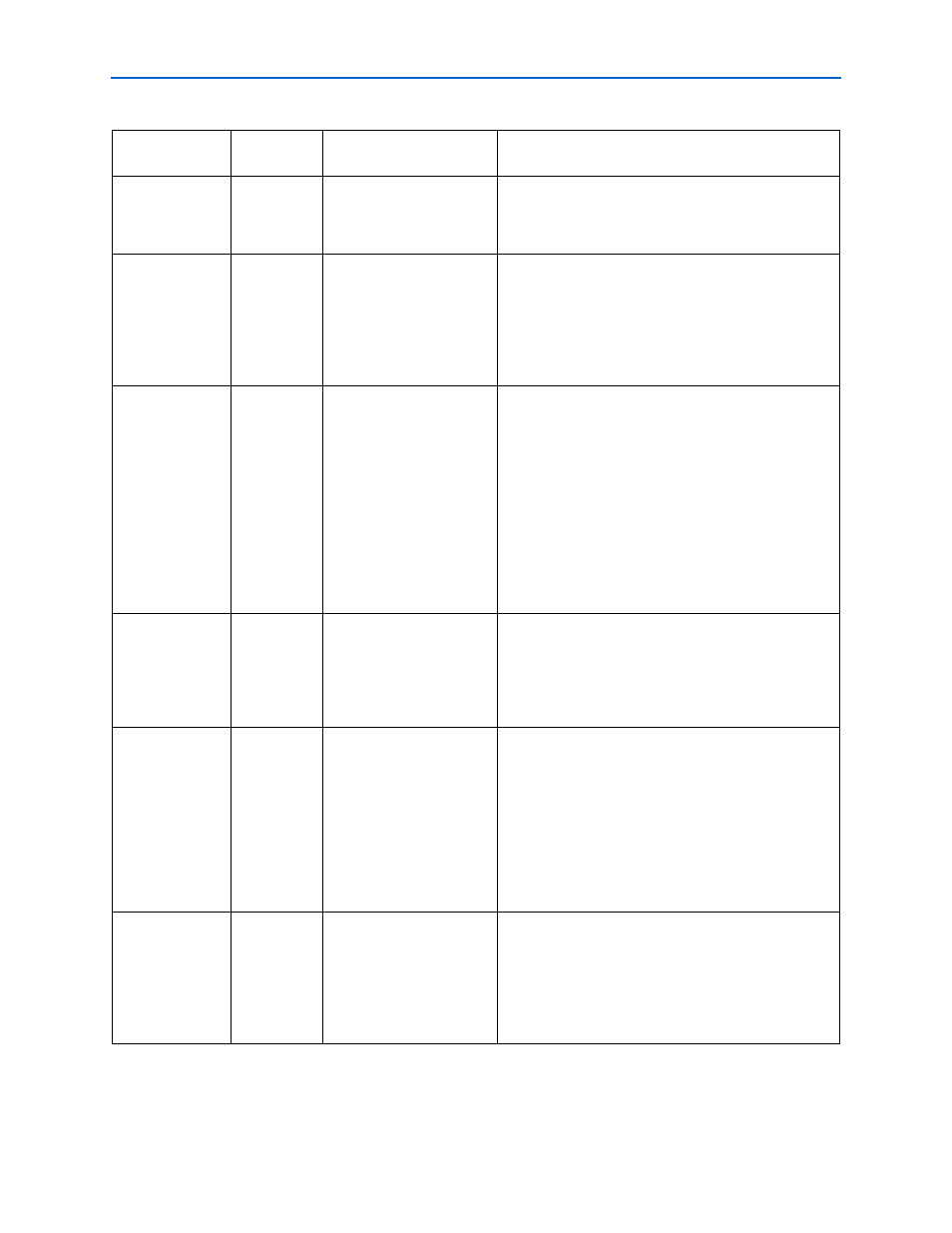

Table 3–4. Options on DQS IN Page (Part 2 of 3)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description