Altera ALTDLL User Manual

Page 41

4–5

Chapter 4: Functional Description

ALTDQ_DQS Megafunction

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

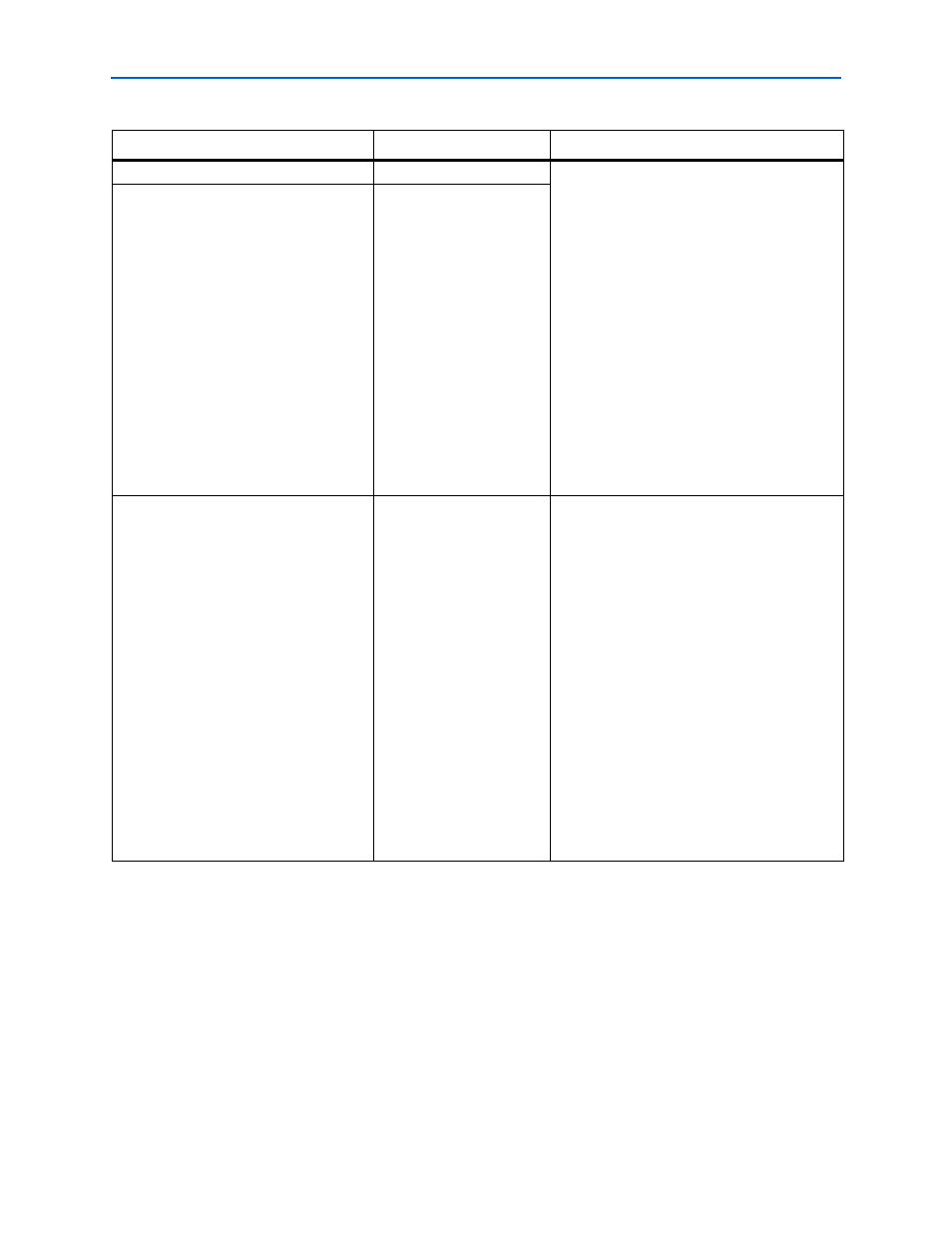

DQS_CONFIG

DQS Configuration Block

A shift register that dynamically changes the

settings of various device configuration bits. The

shift registers power up low.

The

IO_CONFIG

block is used to configure the

settings for all I/O pins. The

IO_CONFIG

block

cannot configure the dynamic delay chains on

the OCT path or on the DQS input path (D2,

D3_0, D3_1, D4,D5 OCT, and D6 OCT) that are

controlled by the

DQS_CONFIG

block.

The

DQS_CONFIG

block is used to configure

the settings of the DQ/DQS I/O pins.

Note that these blocks are only available for

Stratix III and Stratix IV devices.

For more information about the

DQS_CONFIG

/

IO_CONFIG

blocks, refer to

“DQS_CONFIG / IO_CONFIG Block” on

page 4–22

IO_CONFIG

I/O Configuration Block

IO_CLOCK_DIVIDER

I/O Clock Divider Block

Represents a divide-by-2 clock divider for

transferring data to the core at one half the

speed of the I/O input or output clock. Each

divider feeds up to six pins (a ×4 DQS group) in

the device. To feed wider DQS groups, you need

to chain multiple clock dividers together by

feeding the

slaveout

output of one divider to

the

masterin

input of the neighboring pins'

divider.

The

IO_CLOCK_DIVIDER

block is used in the

DQ and DQS input paths when you enable the

Use half-rate components option in the

parameter editor.

Note that this block is only available for

Stratix III and Stratix IV devices.

For more information about this block, refer to

the I/O Element (IOE) Registers section in the

External Memory Interfaces chapter of the

respective device handbooks.

Table 4–2. Common Blocks in the DQ/DQS Input and Output Paths (Part 2 of 2)

Block Name

Description