Altera ALTDLL User Manual

Page 94

Chapter 4: Functional Description

4–58

Design Example: Implementing Half-Rate DDR2 Interface in Stratix III Devices

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

provides the description for each block in the design example.

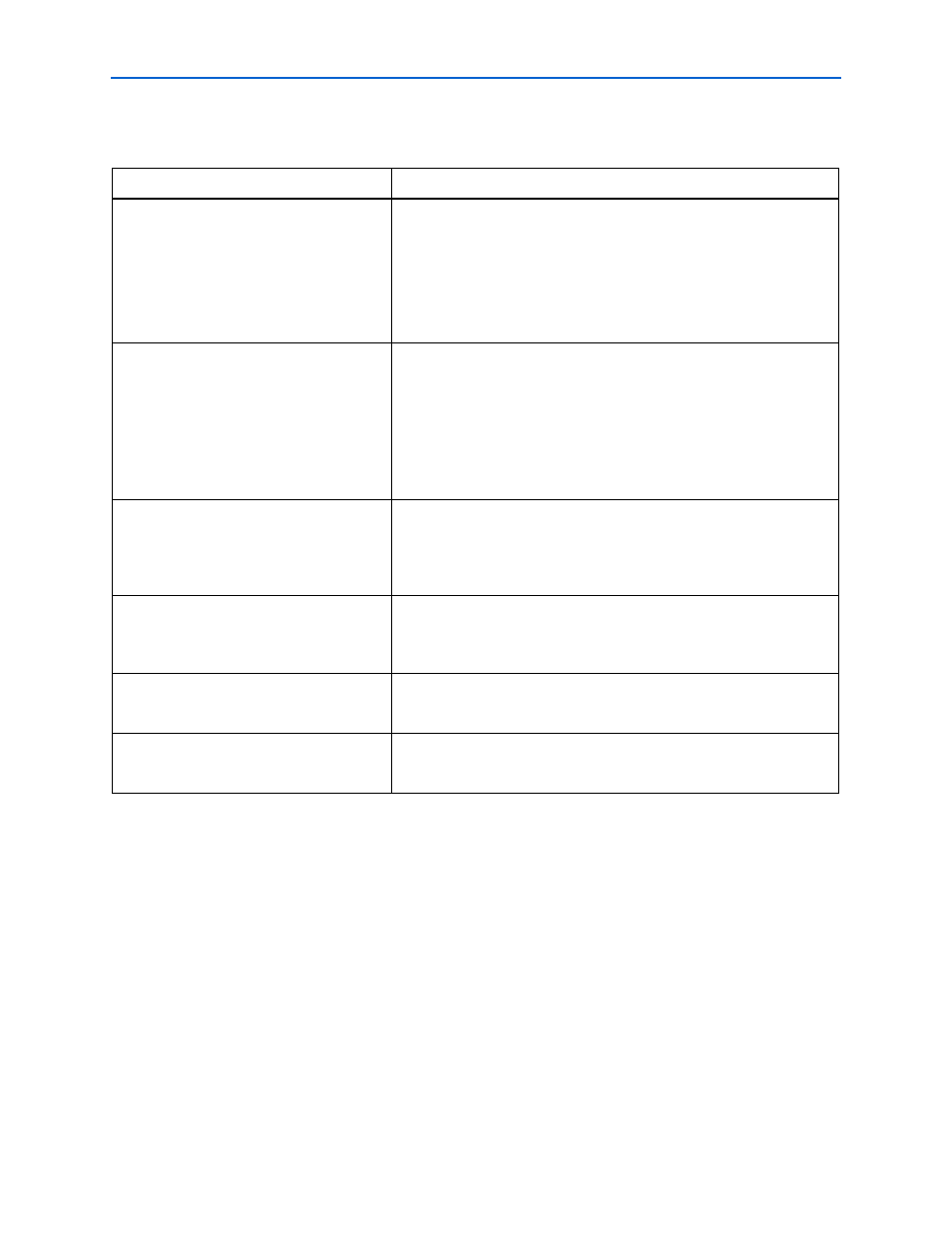

Table 4–37. Blocks in Design Example

Block Name

Description

pll_inst:inst1

This block represents the Stratix III PLL with the following settings:

■

inclk

= 200 MHz

■

c0

= 3,000 ps, 50% duty cycle

■

c1

= 3,000 ps, 50% duty cycle

■

c2

= 3,000 ps, 50% duty cycle

■

c3

= 6,000 ps, 50% duty cycle

dll_inst:inst5

This block represents the DLL circuitry used during a read from the

external memory. This block is clocked by the PLL with the following

settings:

■

delay chain length = 10

■

delay buffer mode = High

■

input frequency = 333 MHz

■

jitter reduction = Turned off

dq_dqs_inst:inst

This block represents the DQ and DQS circuitry that interfaces with the

external memory. The settings are specified in the input.txt file. The block

is customized for a half-rate operation and represents the interface

between the FPGA core and the I/O buffers that are connected to the

external memory pins.

dqs_iobuf_inst:inst2

This block represents the bidirectional I/O buffer that is used as the DQS

strobe/clock signal for interfacing with the external memory. This block is

in differential mode and is 1 bit wide. It is connected to the

dq_dqs_inst

block.

bidir_dq_iobuf_inst:inst3

This block represents the bidirectional I/O buffer that is used as the DQ

data signals for interfacing with the external memory. This block is 8 bits

wide. It is connected to the

dq_dqs_inst

block.

output_dq_iobuf_inst:inst4

This block represents the output I/O buffer that is used as the DQ data

signals for interfacing with the external memory. This block is 1 bit wide. It

is connected to the

dq_dqs_inst

block.