Delay chains, Delay chains –15, Delay – Altera ALTDLL User Manual

Page 51: Delay chains” on

4–15

Chapter 4: Functional Description

Delay Chains

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

Delay Chains

The ALTDQ_DQS megafunction uses various types of delay chains. You can control

delay chains dynamically to provide a better sampling window for external memory

interfaces.

shows the delay chain type and their respective settings.

1

Each step value is either 50 or 400 ps. Setting the number of stages in the delay chain

to 10 means 10 × 50 ps = 500 ps of delay.

1

The minimum delay value factors in only variable delays, but not the intrinsic delay

present in the delay chain. For more information about intrinsic delays, refer to the

respective Arria II GX, HardCopy III, HardCopy IV, Stratix III, and Stratix IV device

handbook or data sheet.

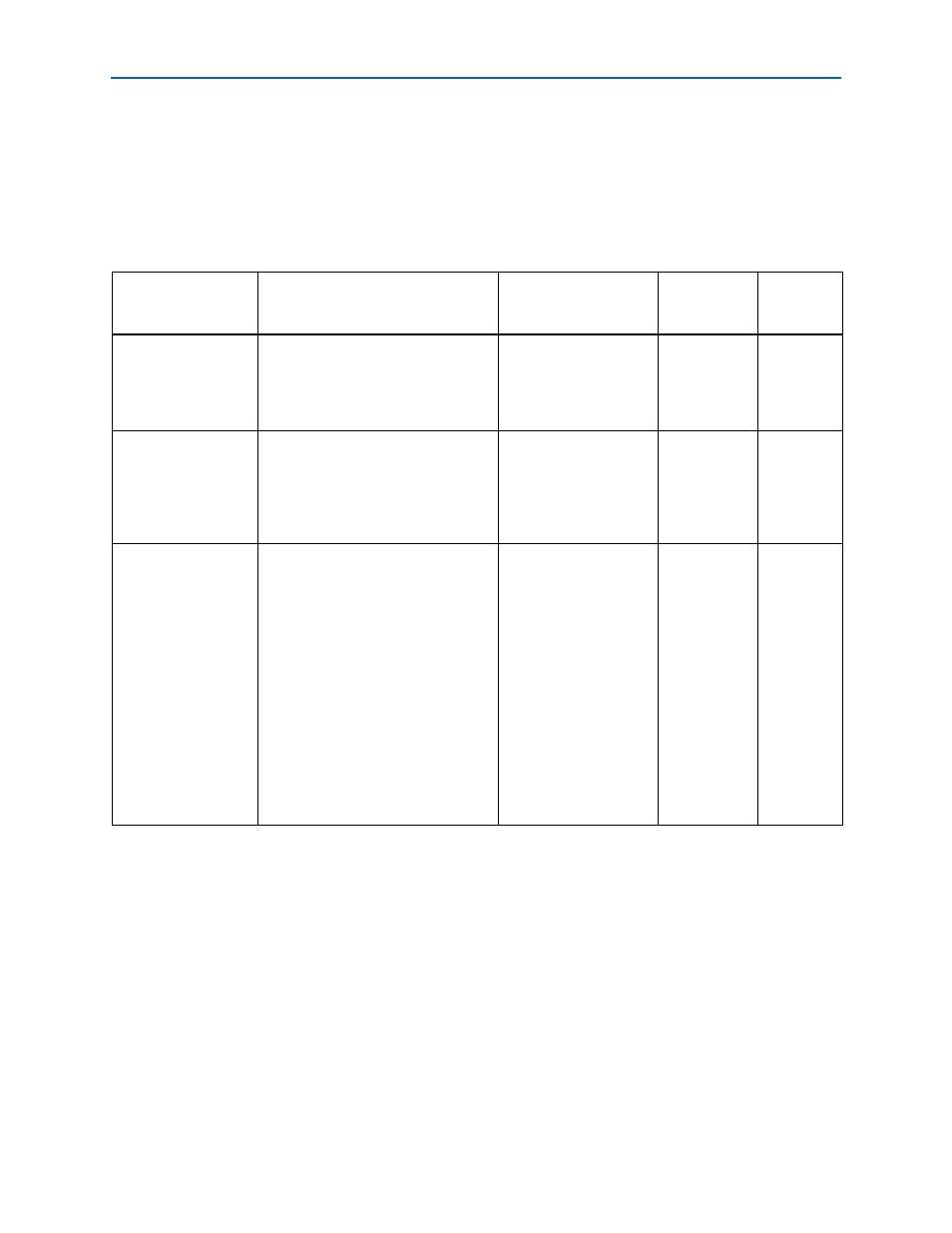

Table 4–8. Delay Elements and Settings

Delay Chain Type

Function

Possible Settings

Step Value

(ps)

Maximum

Delay Value

(ps)

D1

Tunes the DQ delay (read calibration) in

DDR applications.

There are 16 possible

settings for this delay

chain because the delay

control in the chain is

4 bits wide.

50

0

D5 and D5 OCT

D5 is the output register-to-I/O buffer

delay. D5 OCT is the OCT to I/O buffer

delay. These delay chains are for write

calibration in DDR applications. D5 is

cascaded together with D6 to generate

the sum of delays.

There are 16 possible

settings for this delay

chain because the delay

control in the chain is

4 bits wide.

50

0

D6 and D6 OCT

D6 is the output register-to-I/O buffer

delay. D6 OCT is the OCT to I/O buffer

delay. This delay chain is used to

reduce simultaneous switching noise

(

SSN). These delay chains can be

adjusted on a group basis for

non-DDR3 applications. This delay

chain works with a write-leveling clock

to adjust the delay among groups for

DDR3 applications. D6 is cascaded

together with D5 to generate the sum

of delays.

For more information about reducing

SSN, refer to

.

There are 8 possible

settings for this delay

chain because the delay

control in the chain is

3 bits wide.

50

0