Altera ALTDLL User Manual

Page 47

4–11

Chapter 4: Functional Description

ALTDQ_DQS Megafunction

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

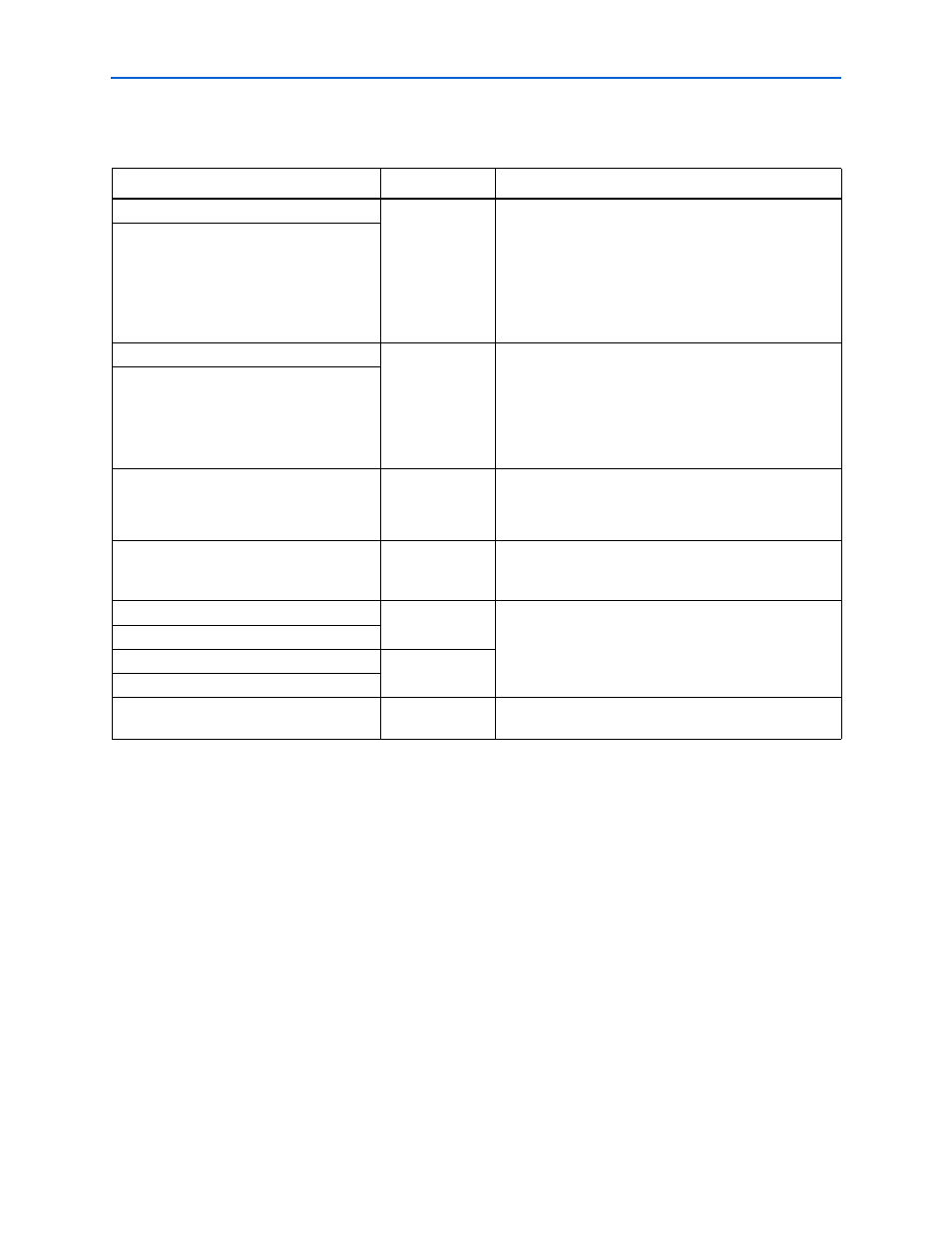

The DQ output and OE path consist of the following blocks:

Table 4–5. DQ Output and OE Path

Block

Name

Description

<IO>

_OUTPUT_FF

DQ output

register blocks

Sends data directly to the external memory DQ pins

during a write operation through the output buffer. These

blocks are clocked by the DQ write clock.

The <IO>

_OUTPUT_FF

block represents a group of

flip-flop registers in the DQ output path.

The <IO>

_OUTPUT_DDIO_OUT

represents a group of

double data rate output registers in the DQ output path.

<IO>

_OUTPUT_DDIO_OUT

<IO>

_OE_FF

DQ output enable

register blocks

Sends output enable signal to the output buffer. These

blocks are clocked by the DQ write clock.

The <IO>

_OE_FF

block represents a group of flip-flop

registers in the DQ OE path.

The <IO>

_OE_DDIO_OE

represents a group of double

data rate registers in the DQ OE path.

<IO>

_OE_DDIO_OE

<IO>

_OUTPUT_HR_DDIO_OUT_HIGH

and

<IO>

_OUTPUT_HR_DDIO_OUT_LOW

Half-rate output

register block

Represents the DDIO registers that are used to transfer

DQ signals from the core during half-rate write operation.

These blocks are clocked by the DQ write clock.

<IO>

_OE_HR_DDIO_OUT

Half-rate output

enable register

block

Represents the DDIO registers that are used to transfer

half-rate DQ output enable signals to the output buffer.

<IO>

_OUTPUT_DELAY_CHAIN1

(D5)

DQ output delay

chains

For more information about the DQ output and OE delay

chains, refer to

<IO>

_OUTPUT_DELAY_CHAIN2

(D6)

<IO>

_OE_DELAY_CHAIN1

(D5)

DQ OE delay

chains

<IO>

_OE_DELAY_CHAIN2

(D6)

IO_CONFIG

I/O Configuration

Block

For more information about the

IO_CONFIG

block, refer

to