50g interlaken ip core clock signals, Ip core reset, 50g interlaken ip core clock signals -5 – Altera 50G Interlaken MegaCore Function User Manual

Page 31: Ip core reset -5

50G Interlaken IP Core Clock Signals

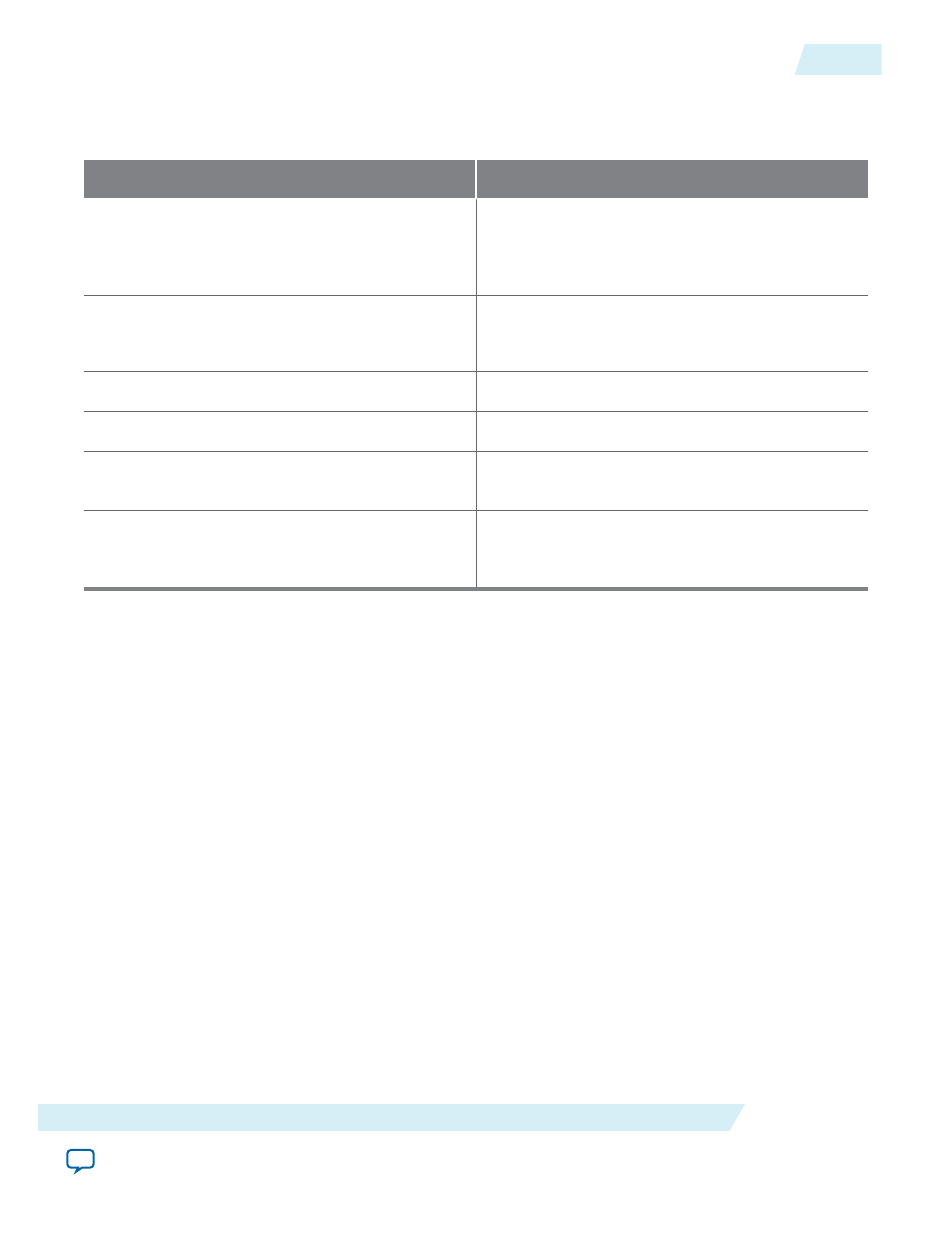

Table 4-1: 50G Interlaken IP Core Clocks

Clock Name

Description

pll_ref_clk

Reference clock for the RX transceiver PLL in IP

core variations that target an Arria 10 device.

Reference clock for RX and TX transceiver PLLs in

all other variations.

tx_serial_clk[NUM_LANES–1:0]

Clocks for the individual transceiver channels in

50G Interlaken IP core variations that target an

Arria 10 device.

rx_usr_clk

Clock for the receive application interface.

tx_usr_clk

Clock for the transmit application interface.

mm_clk

Management clock for 50G Interlaken IP core

register access.

reconfig_clk

Management clock for Arria 10 hard PCS register

access, including access for Arria 10 transceiver

reconfiguration and testing features.

If you choose to instantiate the optional out-of-band flow control blocks, your 50G Interlaken MegaCore

function has additional clock domains.

Related Information

Out-of-Band Flow Control Block Clocks

Comprehensive list of out-of-band flow control block clocks and information about their expected

frequencies.

IP Core Reset

The 50G Interlaken IP core variations have a single asynchronous reset, the

reset_n

signal. The

50G Interlaken IP core manages the initialization sequence internally. After you assert

reset_n

low, the

IP core automatically goes through the entire reset sequence.

Note: Altera recommends that you hold the

reset_n

signal low for at least the duration of two

mm_clk

cycles, to ensure the reset sequence proceeds correctly.

UG-01140

2015.05.04

50G Interlaken IP Core Clock Signals

4-5

Functional Description

Altera Corporation