Altera 50G Interlaken MegaCore Function User Manual

Page 76

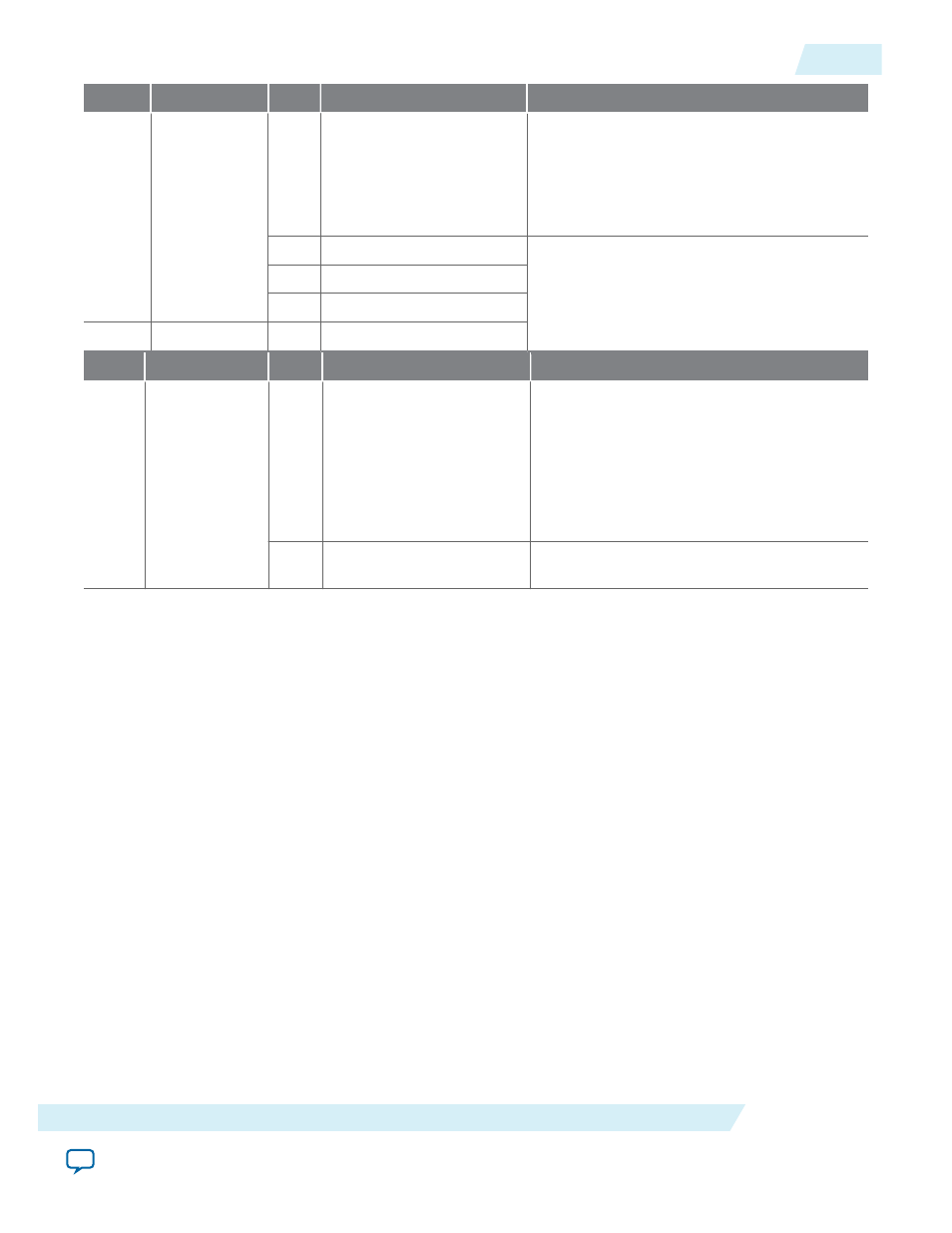

TX

Register Offset

Bits

Meaning

Action

2

0x7

[2]

Invert TX channels

Set this bit to the value of 0 to specify that

the outgoing PRBS be inverted, or set this bit

to the value of 1 to specify that the outgoing

PRBS not be inverted. The default value of

this register field is 0. By default, the

outgoing PRBS is inverted.

[5]

Enable PRBS9

Set one of these bits to the value of 1, and the

others to the value of 0, to select the TX

polynomial.

[6]

Enable PRBS15

[7]

Enable PRBS23

3

0x8

[4]

Enable PRBS31

RX

Register Offset

Bits

Meaning

Action

1

0xA

[4]

Invert RX channels

Set this bit to the value of 0 to specify that

the PCS should expect the incoming PRBS

to be inverted, or set this bit to the value of

1 to specify that the PCS should not expect

the incoming PRBS to be inverted. The

default value of this bit is 0. In loopback

mode, you should set this bit to match the

setting in the PRBS transmitter.

[7]

Enable RX PRBS clock

Set this bit to the value of 1 to enable the RX

PRBS clock.

UG-01140

2015.05.04

Setting up PRBS Mode in Arria 10 Devices

8-5

50G Interlaken IP Core Test Features

Altera Corporation