50g interlaken ip core register map, 50g interlaken ip core register map -1 – Altera 50G Interlaken MegaCore Function User Manual

Page 63

50G Interlaken IP Core Register Map

6

2015.05.04

UG-01140

The 50G Interlaken IP core control registers are 32 bits wide and are accessible to you using the

management interface, an Avalon-MM interface which conforms to the Avalon Interface Specifications.

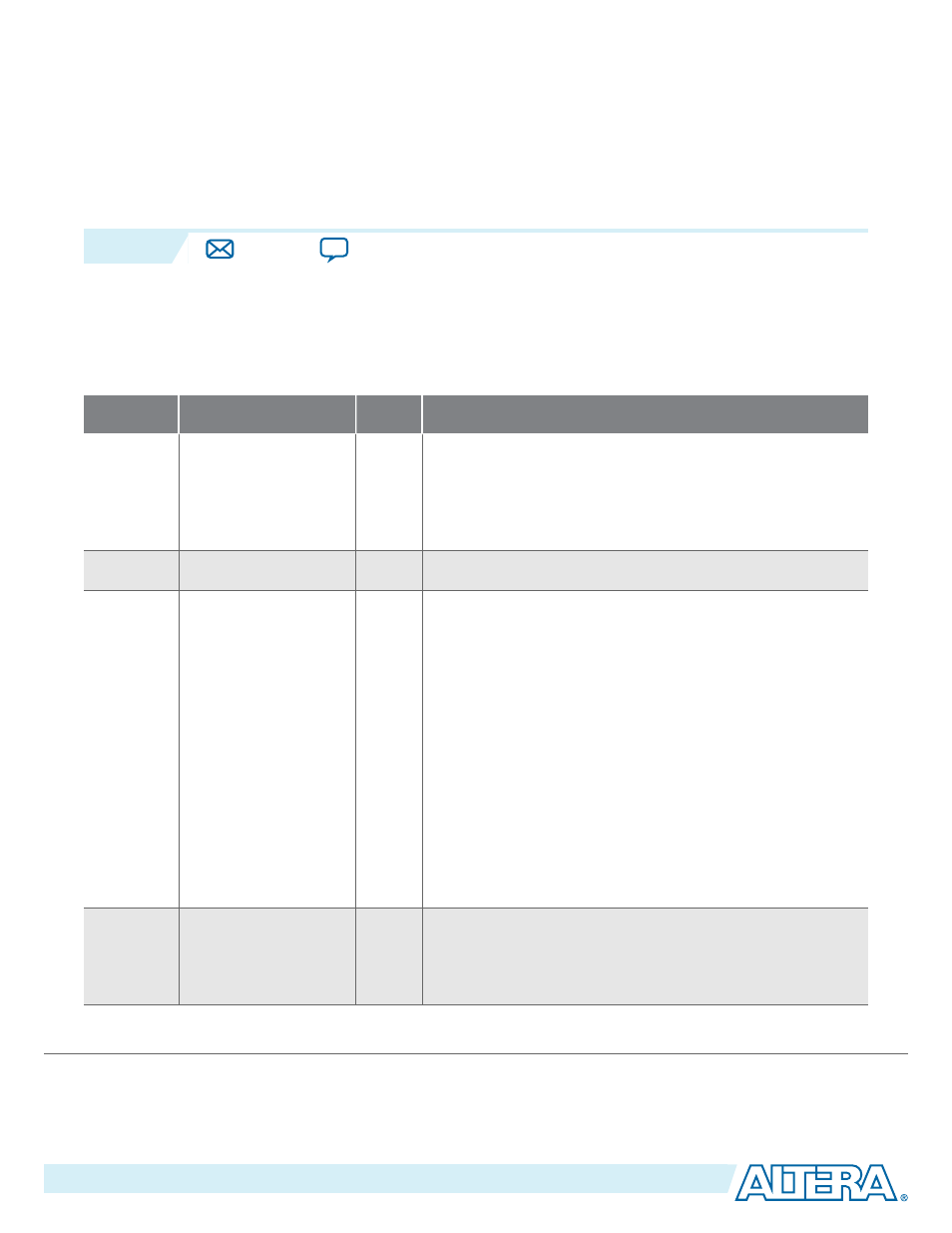

This table lists the registers available in the IP core. All unlisted locations are reserved.

Table 6-1: 50G Interlaken IP Core Register Map

Offset

Name

R/W

Description

9'h0

PCS_BASE

RO

[31:8] – Constant “HSi” ASCII

[7:0] – version number

Despite its name, this register does not encode the hard PCS

base address.

9'h1

LANE_COUNT

RO

Number of lanes

9'h2

TEMP_SENSE

RO

Device temperature according to the internal temperature

sensing diode.

[7:0] – the temperature in degrees Fahrenheit

[15:8] – the temperature in degrees Celsius

For example, when the temperature is 54 degrees Celsius

(130 degrees Fahrenheit), the value of the register is 0x3682.

To interpret this register value, you read 0x36 (decimal 54)

to be the temperature in degrees Celsius, and you read 0x82

(decimal 130) to be the temperature in degrees Fahrenheit.

This register is invalid in the following IP core variations:

• Variations that target an Arria 10 device

• Variations in which you turn off the hidden parameter

Include Temp Sense

9'h3

ELAPSED_SEC

RO

[23:0] - Elapsed seconds since power up. The IP core

calculates this value from the management interface clock

(

mm_clk

) for diagnostic purposes. During continuous

operation, this value rolls over every 194 days.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134