Altera 50G Interlaken MegaCore Function User Manual

Page 77

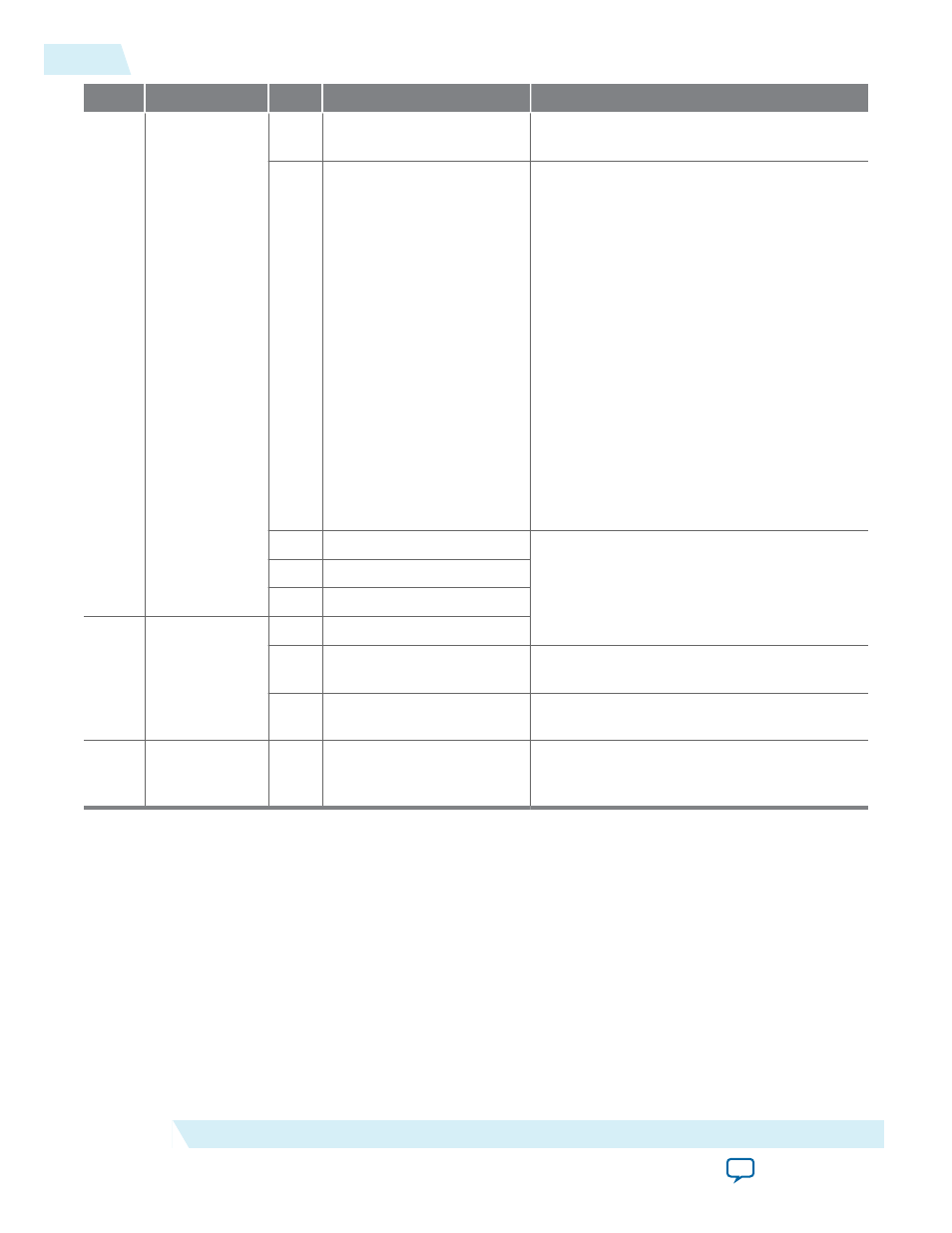

RX

Register Offset

Bits

Meaning

Action

2

0xB

[1]

Enable 10G PCS mode

Set this bit to the value of 1 to specify the

PCS is in 10G mode.

[3:2] Verifier counter threshold

Set this field to the value your design

requires to ensure adequate lead time before

the PRBS checker begins counting PRBS

errors. The field value specifies the wait

time in number of

clk_rx_common

clock

cycles. A counter begins counting

clk_rx_

common

clock cycles after the soft reset, and

triggers the start of PRBS checking when the

specified threshold is reached. This field has

the following valid values:

• 2'b00—Specifies the counter threshold

(the wait time) is 127.

• 2'b01—Specifies the counter threshold is

255.

• 2'b10—Specifies the counter threshold is

511.

• 2'b11—Specifies the counter threshold is

1023.

[5]

Enable PRBS9

Set one of these bits to the value of 1, and

the others to the value of 0, to select the

expected polynomial.

[6]

Enable PRBS15

[7]

Enable PRBS23

3

0xC

[0]

Enable PRBS31

[1]

Confirm 10G PCS mode

Set this bit to the value of 1 to confirm the

PCS is in 10G mode.

[3]

PRBS width select

Set this bit to the value of 0 to specify that

the PRBS width is 64 bits.

4

0x13F

[3:0] RX Deserializer width select Set this field to the value of 4'b1110 to

specify that the data width after deserializa‐

tion is 64 bits.

After you enable the IP core to generate or receive PRBS output, by setting the relevant register field

values for each Interlaken lane, you must perform a soft reset of the transceiver transmitters and receivers.

To perform a soft reset of the transceiver transmitters and receivers, on the 50G Interlaken IP core

management interface, program bit [2] of the 50G Interlaken IP core

RESET

register at offset 0x13 with the

value of 1. On the following

mm_clk

cycle, or later, program the bit 0x13[2] with the value of 0 to clear the

reset. After you reset the transceivers and subsequently clear the reset bit, the IP core immediately begins

transmitting PRBS output on the Interlaken link. You can check the receive PRBS status in the

50G Interlaken IP core PRBS status registers (

RX_PRBS_DONE,

RX_PRBS_ERR,

and

RX_PRBS_COUNT

).

After your testing is complete, you must reset these register bits to their default values and perform the

soft reset to enable normal operation.

8-6

Setting up PRBS Mode in Arria 10 Devices

UG-01140

2015.05.04

Altera Corporation

50G Interlaken IP Core Test Features