B. additional information, Document revision history, Additional information – Altera 50G Interlaken MegaCore Function User Manual

Page 91

Additional Information

B

2015.05.04

UG-01140

This section provides additional information about the document and Altera.

Document Revision History

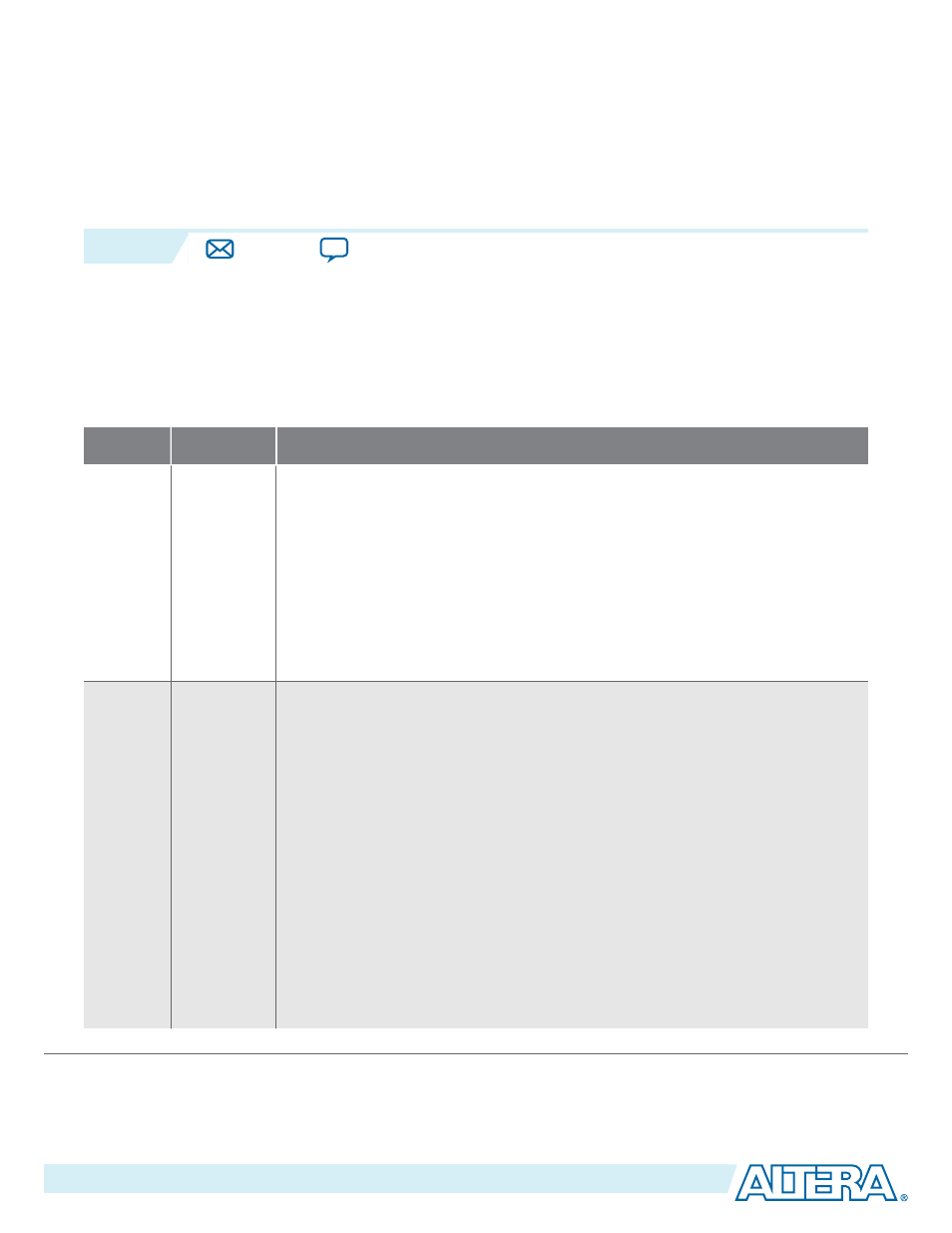

Table B-1: 50G Interlaken MegaCore Function User Guide Revision History

Date

ACDS Version

Changes Made

2015.05

.04

15.0

• Added new TX scrambler seed parameter in new section

on page 3-2. Previously this parameter was hidden (

SCRAM_CONST

) and

unavailable for Arria 10 devices. In the IP core version 15.0 and later, you

must modify the scrambler seed from the parameter editor.

• Improved description of itx_ifc_err output signal in

User Data Transfer Interface Signals

• Improved description of itx_hungry output signal in

Interlaken Link and Miscellaneous Interface Signals

on page 5-8.

• Updated filenames for hidden parameter editing to include the filenames for

Arria 10 variations, in

Modifying Hidden Parameter Values

2014.12

.15

14.1

• Updated release-specific information for the software release v14.1, including

new resource utilization numbers and new Arria 10 speed grade notation and

information. Resource utilization numbers improved by 20% in the v14.0

release.

• Updated for new Quartus II IP Catalog, which replaces the MegaWizard Plug-

In Manager starting in the Quartus II software v14.0. Changes are located

primarily in Getting Started with the 50G Interlaken IP Core chapter.

Reordered the chapter to accommodate the new descriptions.

• Corrected instructions to connect the external TX PLL to include the

tx_cal_

busy

signal, and added example figure to illustrate the required connections

between the IP core and an ATX PLL. Changes are located in Adding the

External PLL section. .

• Added information about the required wait from reset to successful register

access in IP Core Reset section. .

• Corrected width of

reconfig_waitrequest

signal to one bit. This signal has

been a single bit in all versions that support Arria 10 devices, starting with the

IP core version 13.1 Arria 10 Edition.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134