50g interlaken ip core testbench interface signals – Altera 50G Interlaken MegaCore Function User Manual

Page 69

In Arria 10 variations, the example design includes external TX PLLs. You can examine the clear text files

to view sample code that implements one possible method to connect external PLLs to the 50G Interlaken

IP core.

The Arria 10 example design packs six Interlaken lanes in a transceiver block, and connects all of the

channels in the same transceiver block to a single ATX PLL. The IP core connects each ATX PLL to the

50G Interlaken IP core

tx_pll_locked

and

tx_pll_powerdown

ports. This simple connection model is

only one of many options available to you for configuring and connecting the external PLLs in your

50G Interlaken design.

50G Interlaken IP Core Testbench Interface Signals

on page 7-2

on page 7-3

Running the Testbench With the Example Design

on page 7-3

50G Interlaken IP Core Testbench Interface Signals

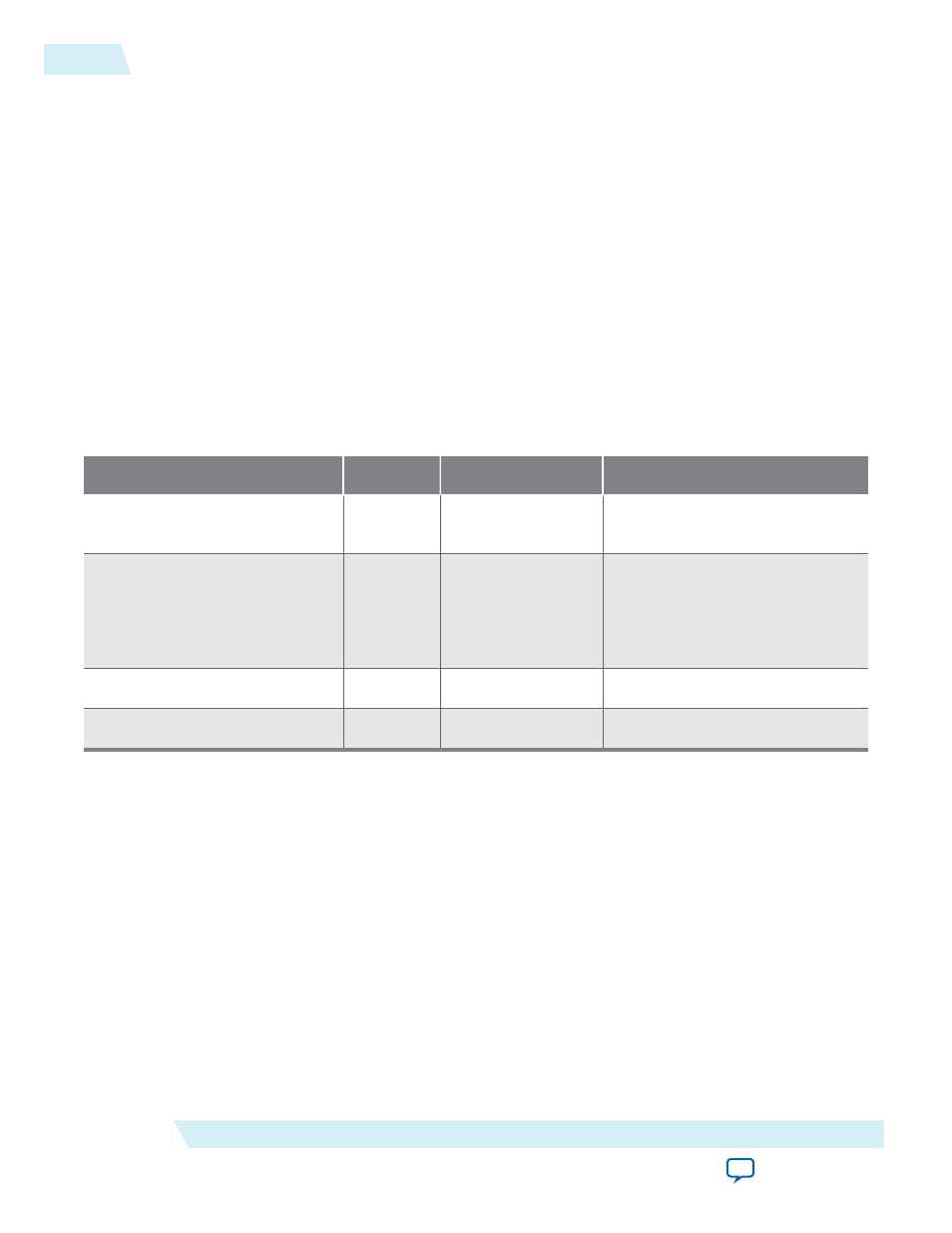

Table 7-1: 50G Interlaken IP Core TestBench Signals

Port Name

Direction

Width (Bits)

Description

clk50

Input

1

System clock input. Clock

frequency is 50 MHz.

pll_ref_clk

Input

1

Transceiver reference clock.

Drives the RX CDR PLL in Arria

10 variations, and drives both the

TX PLL and the RX PLL in other

variations.

rx_pin

Input

Number of lanes

Receiver SERDES data pin.

tx_pin

Output

Number of lanes

Transmit SERDES data pin.

Related Information

50G Interlaken IP Core Clock Interface Signals

Lists the valid PLL reference clock frequencies.

7-2

50G Interlaken IP Core Testbench Interface Signals

UG-01140

2015.05.04

Altera Corporation

50G Interlaken IP Core Testbench