Altera 50G Interlaken MegaCore Function User Manual

Page 65

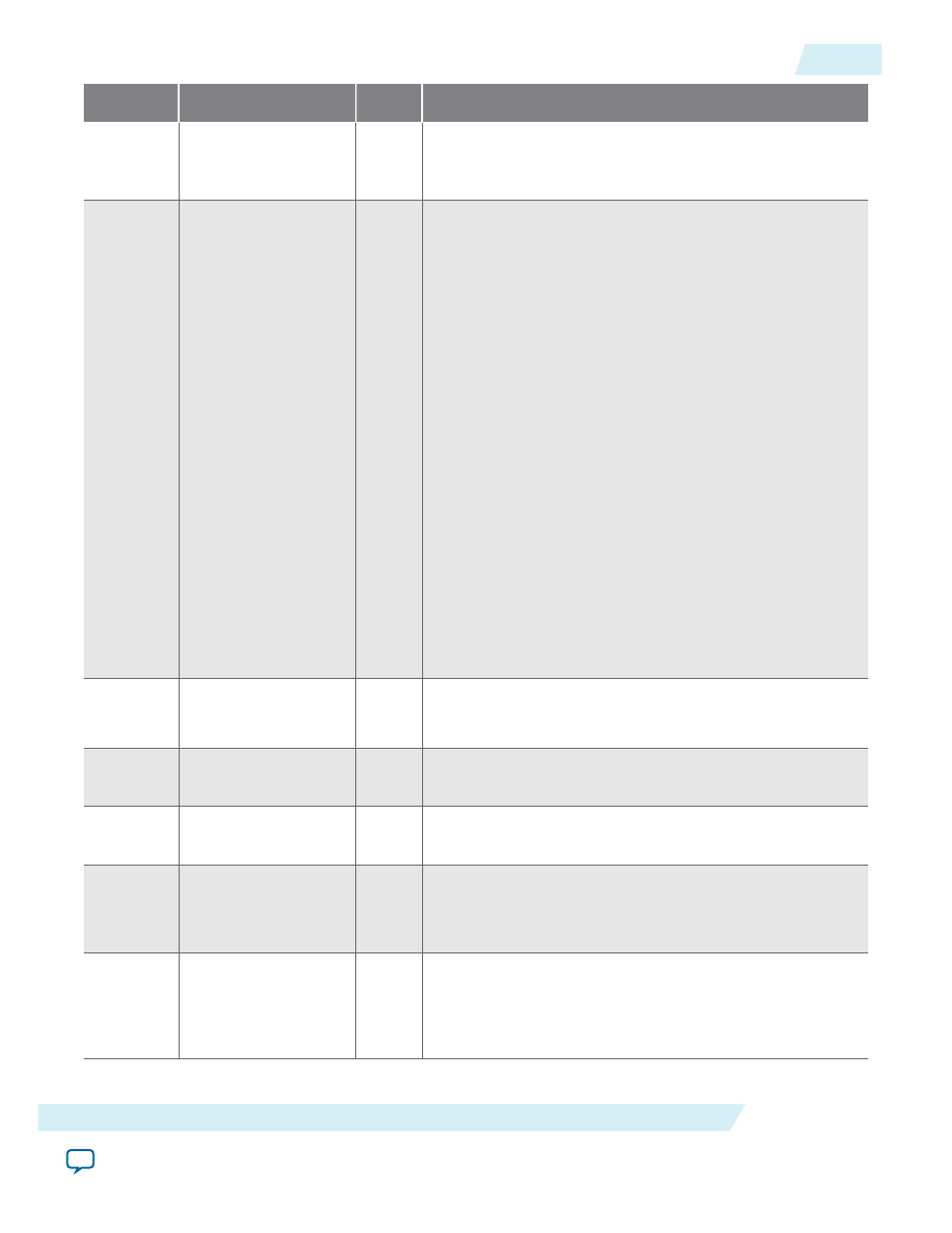

Offset

Name

R/W

Description

9'h12

LOOPBACK

RW

[NUM_LANES–1:0] – For each lane, write a 1 to activate

internal TX to RX serial loopback mode, or write a 0 to

disable the loopback for normal operation.

9'h13

RESET

RW

Bit 9 : 1 = Force lock to data mode

Bit 8 : 1 =Force lock to reference mode

Bit 7 : 1 = Synchronously clear the TX-side error counters

and sticky flags

Bit 6 : 1 = Synchronously clear the RX-side error counters

and sticky flags

Bit 5 : 1 =Program load mode: perform a sequence of DMA

reads. Currently the IP core supports only the value of 1'b0,

indicating a processor controls the read operations.

Bit 4 : 1 = Ignore the RX analog reset

Bit 3 : 1 = Reset the soft microcontroller

Bit 2 : 1 = Reset the transmitter and the receiver

Bit 1 : 1 = Reset the receiver

Bit 0 : 1 =Ignore RX digital resets

The normal operating state for this register is all zeroes, to

allow automatic reset control. These bits are intended

primarily for hardware debugging use. Bit 2 is a good

general purpose soft reset. Bits 6 and 7 are convenient for

monitoring long stretches of error-free operation.

9'h20

ALIGN

RO

Bit 12 : TX lanes are aligned

Bit 0 : RX lanes are aligned.

9'h21

WORD_LOCK

RO

[NUM_LANES–1:0] – Word (block) boundaries have been

identified in the RX stream.

9'h22

SYNC_LOCK

RO

[NUM_LANES–1:0] – Metaframe synchronization has been

achieved.

9'h23

CRC0

RO

4 bit counters indicating CRC errors in lanes 7,6,5,4,3,2,1,0.

These will saturate at F, and you clear them by setting bit 6

in the RESET register.

9'h24

CRC1

RO

4 bit counters indicating CRC errors in lanes

15,14,13,12,11,10,9,8.

These will saturate at F, and you clear them by setting bit 6

in the RESET register.

UG-01140

2015.05.04

50G Interlaken IP Core Register Map

6-3

50G Interlaken IP Core Register Map

Altera Corporation