Altera 50G Interlaken MegaCore Function User Manual

Page 37

During the SOP cycle (labeled with data value d1) and the cycle that follows the SOP cycle (labeled with

data value d2), you must hold the value of

itx_num_valid[2:0]

at 3'b100. In the following clock cycle,

labeled with data value d3, you must hold the following values on critical input signals to the IP core:

•

itx_num_valid[2:0]

at the value of 3'b011 to indicate the current data symbol contains three 64-bit

words of valid data.

•

itx_eopbits[3]

high to indicate the current cycle is an EOP cycle.

•

itx_eopbits[2:0]

at the value of 3'b011 to indicate that only three bytes of the final valid data word

are valid data bytes.

This signal behavior correctly transfers a data packet with the total packet length of 83 bytes to the IP core,

as follows:

• In the SOP cycle, the IP core receives 32 bytes of valid data (d1).

• In the following clock cycle, the IP core receives another 32 bytes of valid data (d2).

• In the third clock cycle, the EOP cycle, the IP core receives two full words (2 x 8 = 16 bytes) and three

bytes of valid data, for a total of 19 valid bytes.

The total packet length is 32 + 32 + 19 = 83 bytes.

50G Interlaken IP Core Back-Pressured Packet Transfer Example

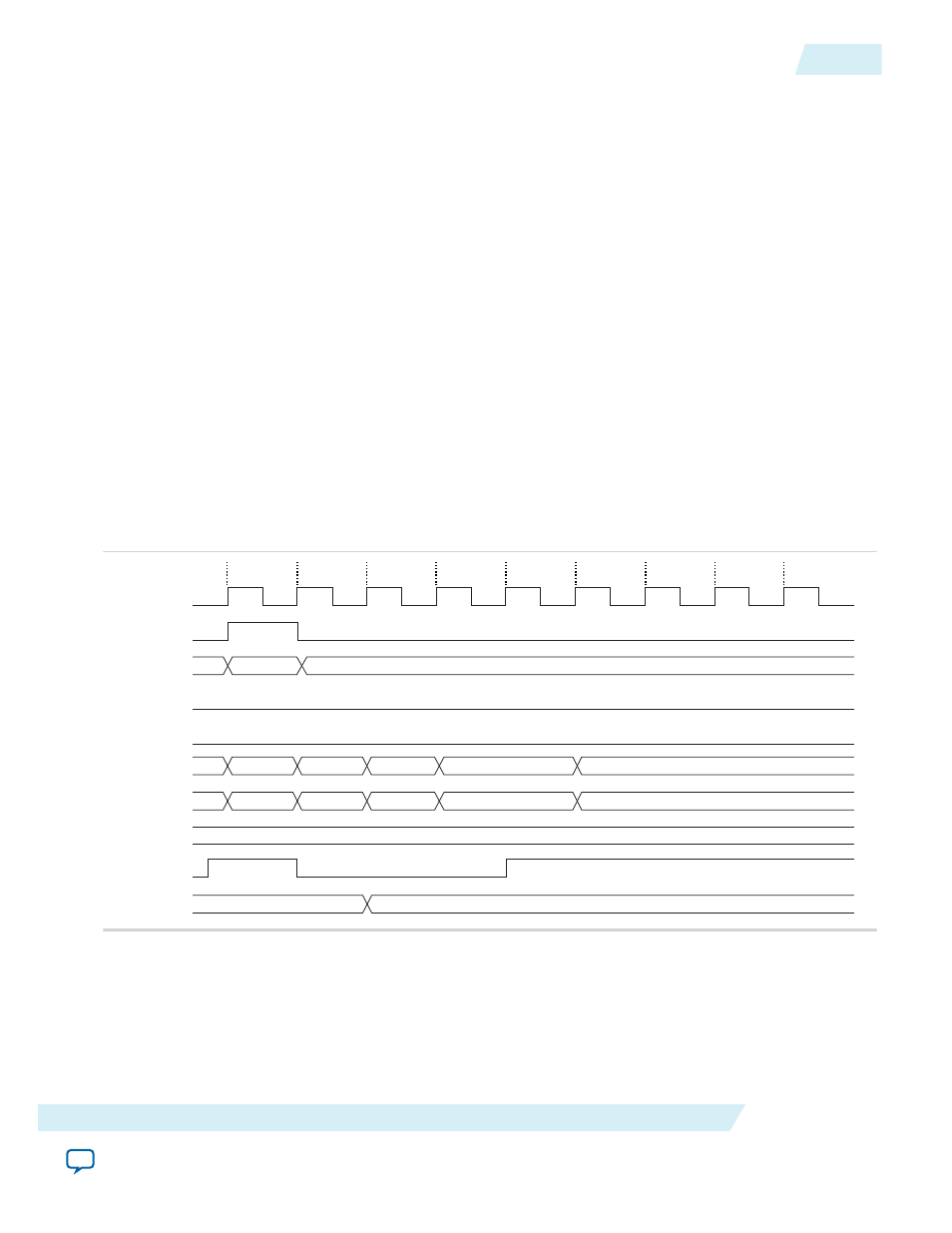

Figure 4-6: Packet Transfer on Transmit Interface with Back Pressure

This example illustrates the expected behavior of the 50G Interlaken application interface transmit signals

during a packet transfer with back pressure.

tx_usr_clk

itx_sop

itx_chan

itx_sob

itx_eob

itx_din_words

itx_num_valid

itx_eopbits

itx_ready

itx_calendar

Cycle 1

Cycle 2

Cycle 3

Cycle 4

Cycle 5

Cycle 6

Cycle 7

Cycle 8

Cycle 9

8’h2

d1

d2

d3

3’b100

3’b100

3’b100

4’b0000

d4

3’b000

3’b100

64’hffff_ffff_ffff_ffff

64’h1111_2222_3333_4444

In this example, the 50G Interlaken IP Core accepts the first four data symbols (128 bytes) of a data

packet. The clock cycles in which the application transfers the data values d2 and d3 to the 50G Interlaken

IP Core are grace-period cycles following the 50G Interlaken IP Core's de-assertion of

itx_ready

.

The 50G Interlaken IP Core supports up to 4 cycles of grace period, enabling you to register the input data

and control signals, as well as the

itx_ready

signal, without changing functionality. The grace period

UG-01140

2015.05.04

50G Interlaken IP Core Back-Pressured Packet Transfer Example

4-11

Functional Description

Altera Corporation