50g interlaken ip core transmit path blocks, 50g interlaken ip core transmit path blocks -13 – Altera 50G Interlaken MegaCore Function User Manual

Page 39

Control Word

Reset Calendar Bit (bit [56])

In-Band Flow Control Bits (bits [55:40])

Second

0

16'b0010001000100010 (16'h2222)

Third

0

16'b0011001100110011 (16'h3333)

Fourth

0

16'b0100010001000100 (16'h4444)

For details of the control word format, refer to the Interlaken Protocol Specification, Revision 1.2.

The 50G Interlaken IP Core supports

itx_calendar

widths of 1, 2, 4, 8, and 16 16-bit calendar pages.

You configure the width in the 50G Interlaken IP Core parameter editor.

By convention, in a standard case, each calendar bit corresponds to a single data channel. However, the

50G Interlaken IP Core assumes no default usage. You must map the calendar bits to channels or link

status according to your specific application needs. For example, if your design has 64 physical channels,

but only 16 priority groups, you can use a single calendar page and map each calendar bit to four physical

channels. As another example, for a different application, you can use additional calendar bits to pass

quality-of-service related information to the Interlaken link partner.

If your application flow-controls a channel, you are responsible for dropping the relevant packet. Altera

supports the transfer of the

itx_calendar

values you provide without examining the data that is affected

by in-band flow control of the Interlaken link.

Related Information

•

50G Interlaken IP Core Back-Pressured Packet Transfer Example

on page 4-11

Example of in-band calendar bits usage on the TX user data transfer interface.

•

50G Interlaken IP Core Transmit Path Blocks

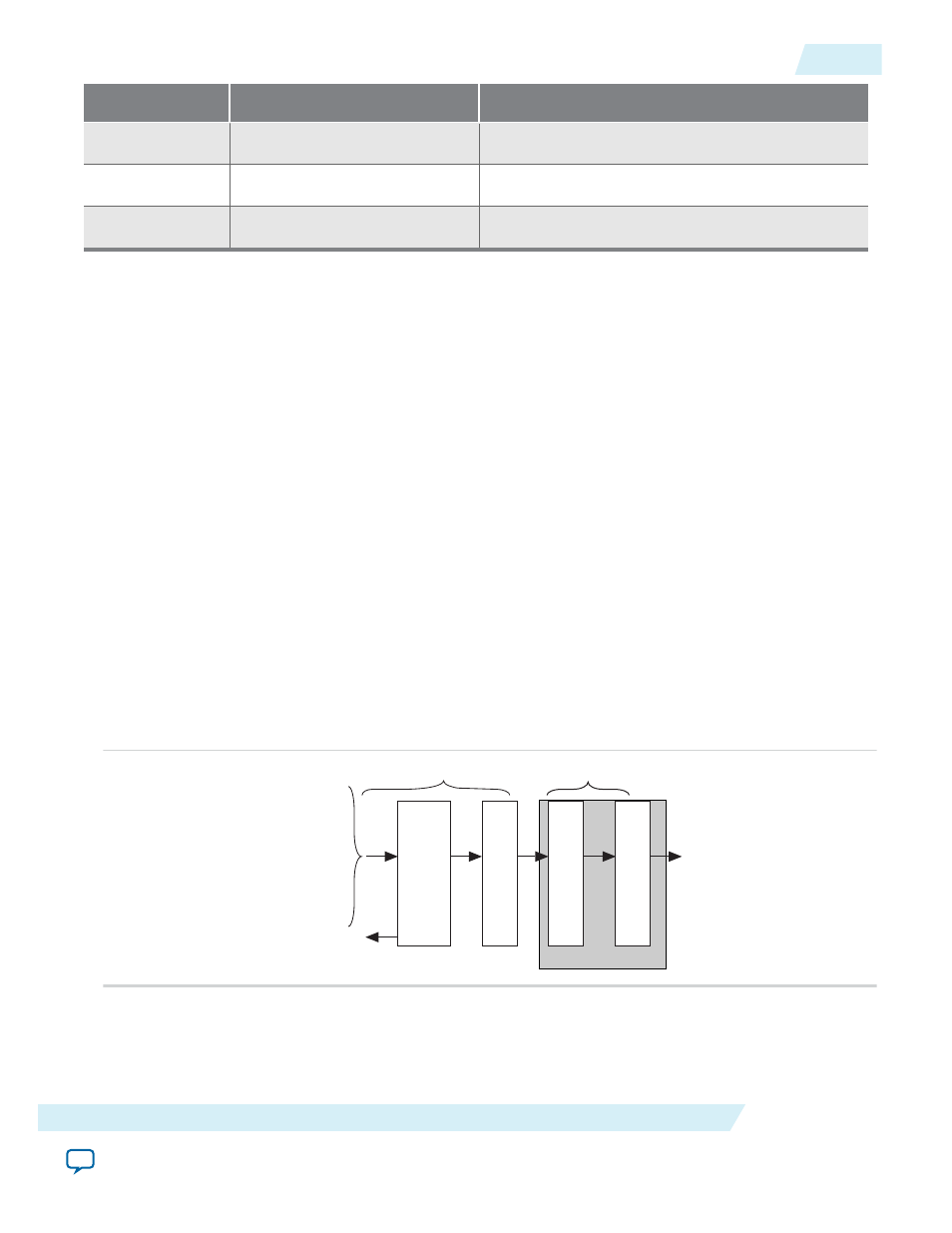

Figure 4-7: 50G Interlaken IP Core Transmit Path

itx_chan[7:0]

itx_num_valid[2:0]

itx_sob

itx_eob

itx_sop

itx_eopbits[3:0]

itx_din_words[255:0]

itx_calendar[16 x n - 1:0]

Transceiver Blocks

TX

PCS

TX

PMA

TX

MAC

TX

Transmit

Buffer

clk_tx_common

tx_pin[m - 1:0]

itx_ready

tx_usr_clk

The 50G Interlaken IP core transmit data path has the following four main functional blocks:

50G Interlaken IP Core TX Transmit Buffer

on page 4-14

UG-01140

2015.05.04

50G Interlaken IP Core Transmit Path Blocks

4-13

Functional Description

Altera Corporation