50g interlaken ip core receive path blocks, 50g interlaken ip core rx pma, 50g interlaken ip core rx pcs – Altera 50G Interlaken MegaCore Function User Manual

Page 45: 50g interlaken ip core rx mac, 50g interlaken ip core receive path blocks -19

50G Interlaken IP Core Receive Path Blocks

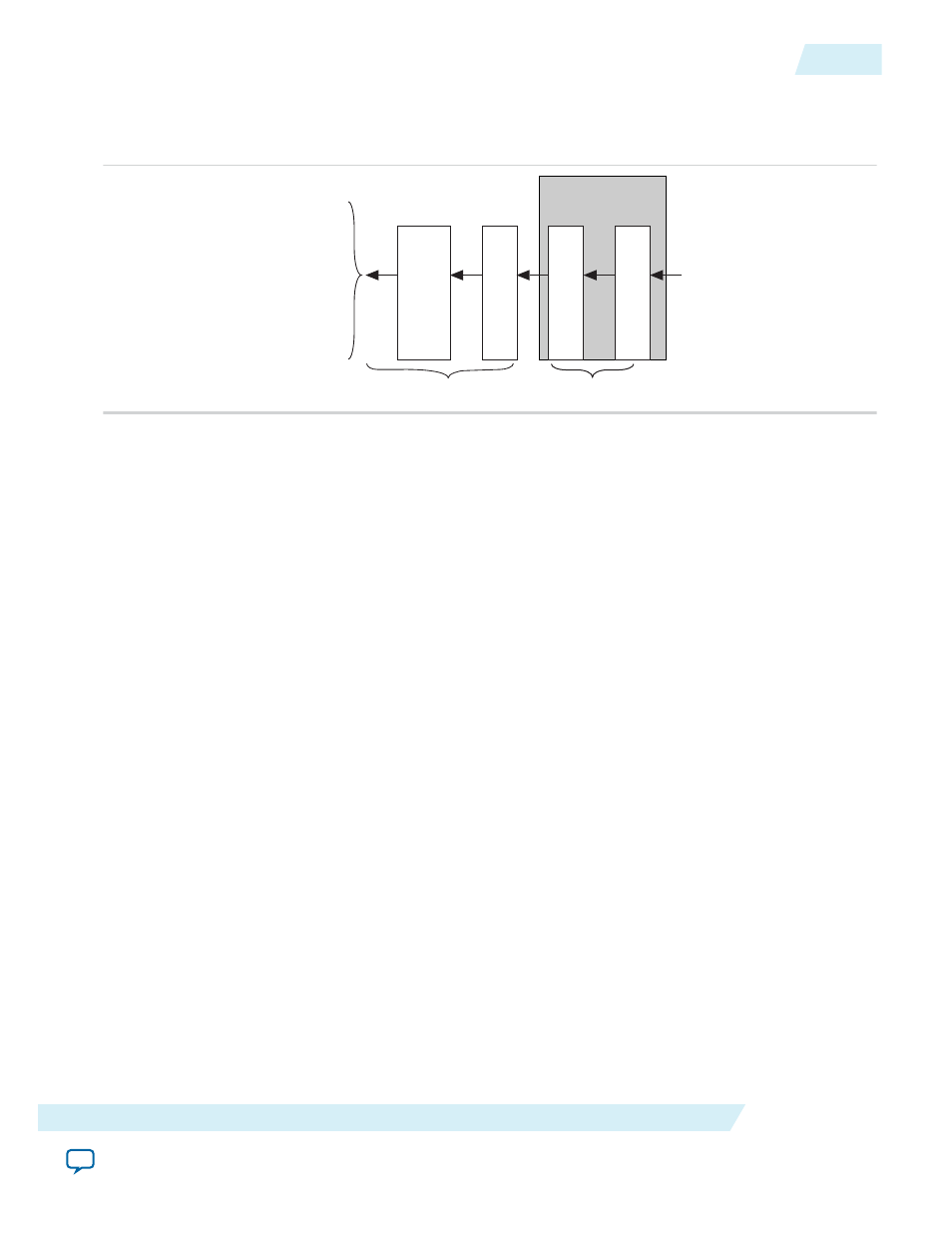

Figure 4-10: 50G Interlaken IP Core Receive Path

irx_chan[7:0]

irx_num_valid[2:0]

irx_sob

irx_eob

irx_sop

irx_eopbits[3:0]

irx_dout_words[255:0]

irx_calendar[16 x n - 1:0]

irx_err

Transceiver Blocks

clk_rx_common

RX

PCS

RX

PMA

RX

MAC

RX

Regroup

rx_pin[m - 1:0]

rx_usr_clk

The 50G Interlaken IP core receive data path has the following four main functional blocks:

on page 4-19

on page 4-19

50G Interlaken IP Core RX Regroup Block

on page 4-20

50G Interlaken IP Core RX PMA

The 50G Interlaken MegaCore function RX PMA deserializes data that the IP core receives on the serial

lines of the Interlaken link.

50G Interlaken IP Core RX PCS

RX PCS logic is an embedded hard macro and does not consume FPGA soft logic elements.

The 50G Interlaken MegaCore function RX PCS block performs the following functions to retrieve the

data:

• Detects word lock and word synchronization.

• Checks running disparity.

• Reverses gearboxing and 64/67B encoding.

• Descrambles the data.

• Delineates meta frame boundaries.

• Performs CRC32 checking.

• Sends lane status information to the calendar and status blocks.

50G Interlaken IP Core RX MAC

To recover a packet or burst, the RX MAC takes data from each of the PCS lanes and reassembles the

packet or burst.

UG-01140

2015.05.04

50G Interlaken IP Core Receive Path Blocks

4-19

Functional Description

Altera Corporation