Altera 50G Interlaken MegaCore Function User Manual

Page 59

If you do not use the management interface, drive the management inputs as follows:

•

mm_clk

must connect to a stable clock. However, the clock signal need not be of unusually high quality.

•

mm_clk_locked

must be tied to zero.

•

mm_read

and

mm_write

must be tied to zero.

If you use the management interface, drive the control lines as shown in the examples and observing the

following constraints:

• During a write operation, you must maintain the the

mm_write

signal asserted for at least two clock

cycles. Back-to-back writes must be separated by at least one clock cycle.

• During a read operation, you must maintain the

mm_read

signal asserted for at least two clock cycles.

Back-to-back reads must be separated by at least one clock cycle.

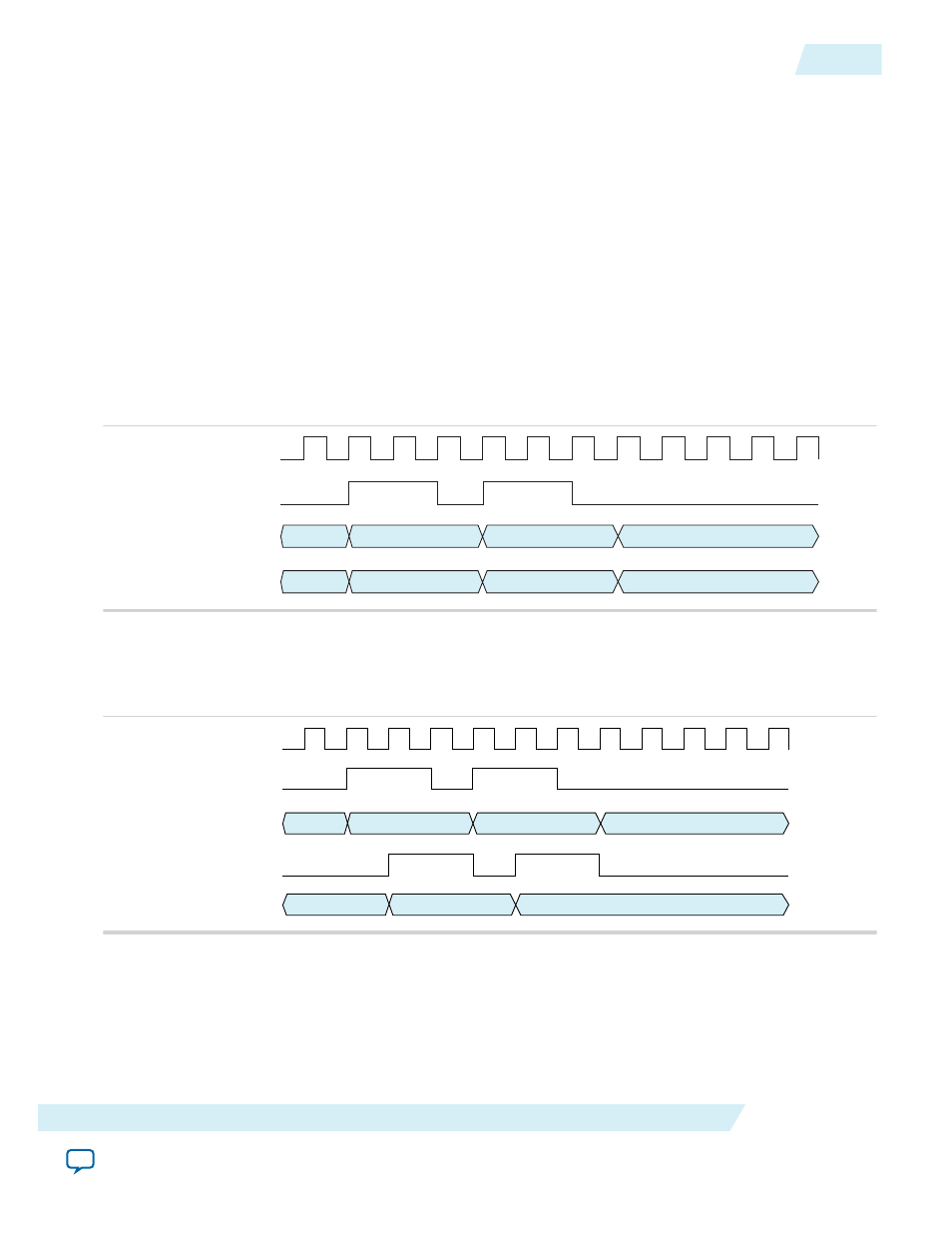

Figure 5-1: 50G Interlaken IP Core Management Interface Write Operation

Shows the timing requirements for a write operation on the 50G Interlaken IP core management

interface.

mm_clk

mm_write

mm_addr[15:0]

mm_wdata[31:0]

Don’t Care

0x0012

0x0013

Don’t Care

Don’t Care

wdata0

wdata1

Don’t Care

Figure 5-2: 50G Interlaken IP Core Management Interface Read Operation

Shows the timing requirements for a read operation on the 50G Interlaken IP core management interface.

The IP core asserts the

mm_rdata_valid

signal one cycle after the

mm_read

signal is asserted.

mm_clk

mm_read

mm_addr[15:0]

mm_rdata_valid

mm_rdata[31:0]

Don’t Care

0x0000

0x0001

Don’t Care

Previous Value

rdata0

rdata1

Related Information

UG-01140

2015.05.04

50G Interlaken IP Core Management Interface

5-13

50G Interlaken MegaCore Function Signals

Altera Corporation