Altera 50G Interlaken MegaCore Function User Manual

Page 90

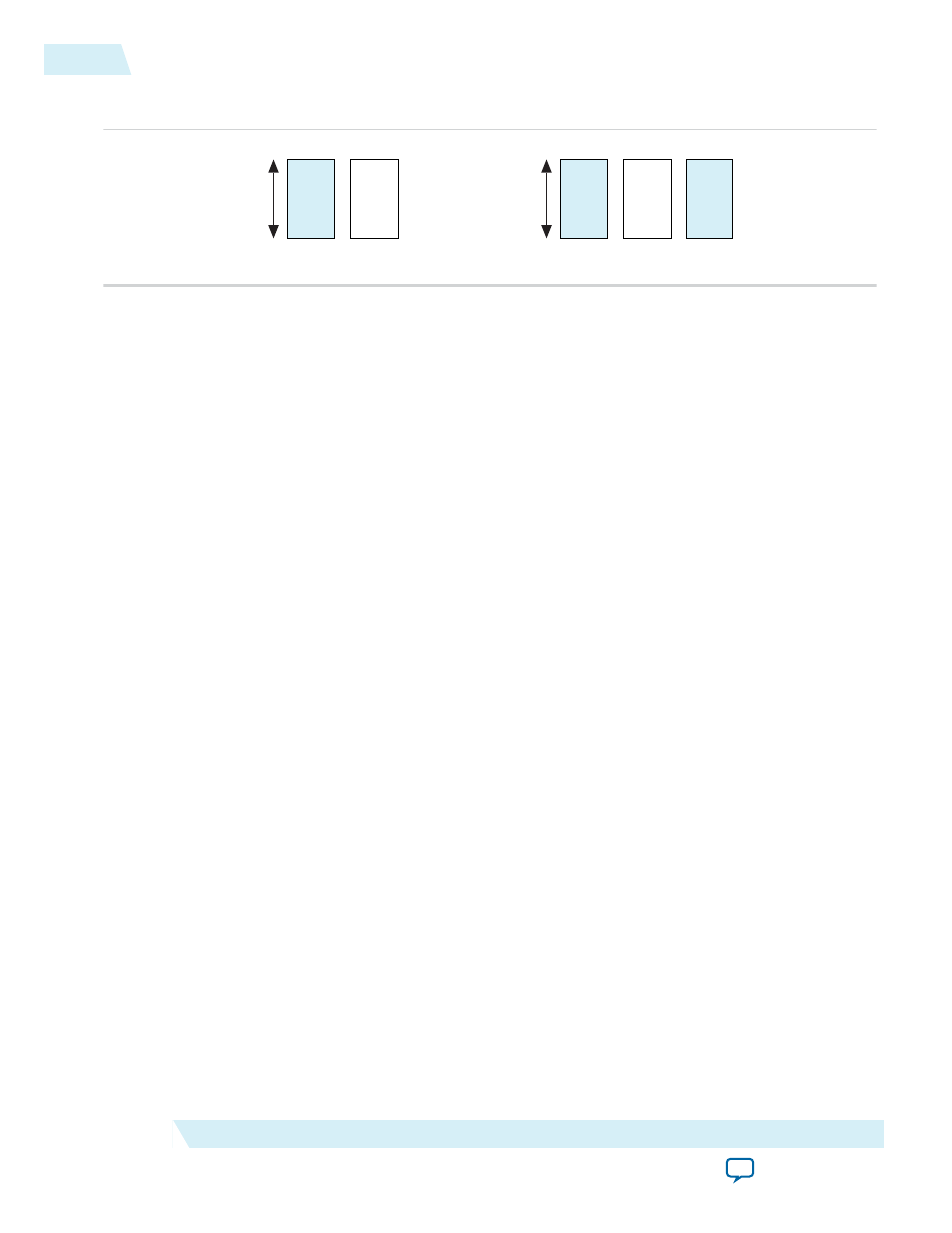

Figure A-2: Packet Processing Requirements

32

Bytes

32

Bytes

64 Bytes at 200 MHz

256

1

2

32

Bytes

32

Bytes

65 - 96 Bytes in 15 ns

256

1 - 32

Bytes

A 65-byte packet comprises (65 + 20) x 8 = 680 bits. Therefore, for traffic that consists mainly of 65-byte

packets, the most inefficient traffic possible, the user interface must handle:

40 x 1,000,000,000 bits/sec ÷ 680 = 58.8 Million packets/sec, or one packet every 17 ns.

Case 2 in the figure shows that the user interface requires three cycles to process each 65-byte packet. At

200 MHz, three cycles take 15 ns, which is a sufficiently small amount of time.

The same calculations applied to lower frequencies yield an average time per packet that is not sufficiently

short. Therefore, 200 MHz is the recommended frequency for the two user data transfer interface clocks

in your 50G Interlaken IP core.

A-2

Performance and Fmax Requirements for 40G Ethernet Traffic

UG-01140

2015.05.04

Altera Corporation

Performance and Fmax Requirements for 40G Ethernet Traffic