Arria 10 external pll interface signals, Arria 10 external pll interface signals -15 – Altera 50G Interlaken MegaCore Function User Manual

Page 61

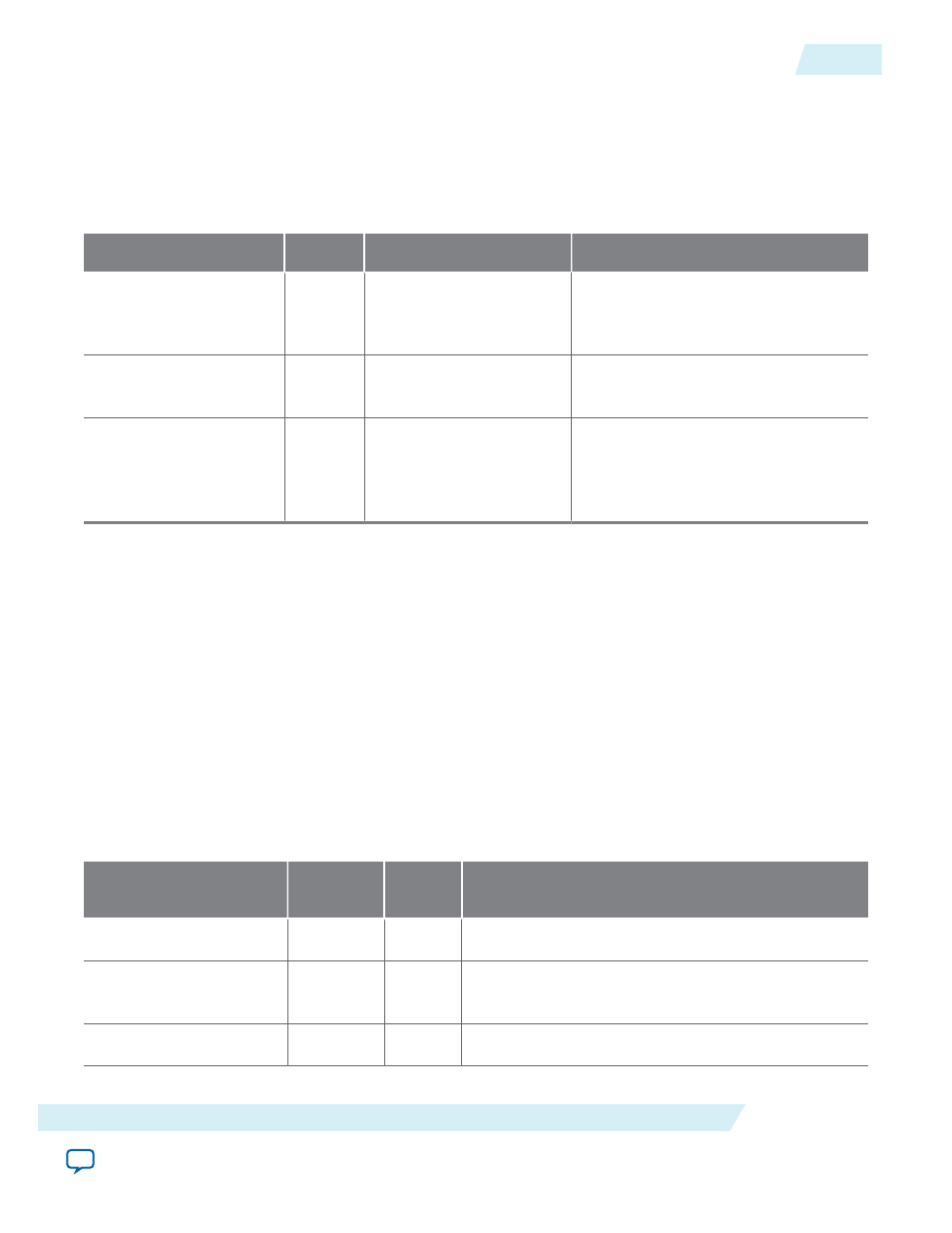

Arria 10 External PLL Interface Signals

50G Interlaken IP core variations that target an Arria 10 device require an external transceiver PLL to

function correctly in hardware. 50G Interlaken IP core variations that target an Arria V or Stratix V

device include the transceiver PLLs and do not require that you configure any additional PLLs.

Table 5-7: 50G Interlaken IP Core Arria 10 External PLL Interface Signals

Signal Name

Direction

Width (Bits)

Description

tx_serial_clk

Input

NUM_LANES

High-speed clock for Arria 10

transceiver channel, provided from

external TX PLL.

tx_pll_locked

Input

1

PLL-locked indication from external

TX PLL.

tx_pll_powerdown

Output

1

Output signal from the IP core

internal reset controller. The IP core

asserts this signal to tell the external

PLLs to power down.

Related Information

on page 2-12

Arria 10 Transceiver Reconfiguration Interface Signals

The 50G Interlaken IP core Arria 10 transceiver reconfiguration interface allows you to communicate

with Arria 10 hard PCS registers. This interface is available only in variations that target an Arria 10

device. You use this interface to reconfigure the transceiver and to take advantage of built-in transceiver

features that the 50G Interlaken IP Core supports for IP core testing. The interface allows you to address a

single register in a single transceiver channel at one time.

The Arria 10 transceiver reconfiguration interface is a typical 32-bit memory-mapped register port. It

complies with the Avalon Memory-Mapped (Avalon-MM) specification defined in the Avalon Interface

Specifications.

Table 5-8: 50G Interlaken IP Core Arria 10 Transceiver Reconfiguration Interface Signals

Signal Name

Direction

Width

(Bits)

Description

reconfig_clk

Input

1

Arria 10 transceiver reconfiguration interface clock.

reconfig_reset

Input

1

Assert this signal to reset the Arria 10 transceiver

reconfiguration interface.

reconfig_read

Input

1

Read access to the Arria 10 hard PCS registers.

UG-01140

2015.05.04

Arria 10 External PLL Interface Signals

5-15

50G Interlaken MegaCore Function Signals

Altera Corporation