2 ecat event request (ecat interrupt), 3 clearing interrupts accidentally, Ecat event request (ecat interrupt) – BECKHOFF EtherCAT Technology Section I User Manual

Page 103: Clearing interrupts accidentally, Figure 42: ecat interrupt masking

Interrupts

Slave Controller

– Technology

I-83

12.2 ECAT Event Request (ECAT Interrupt)

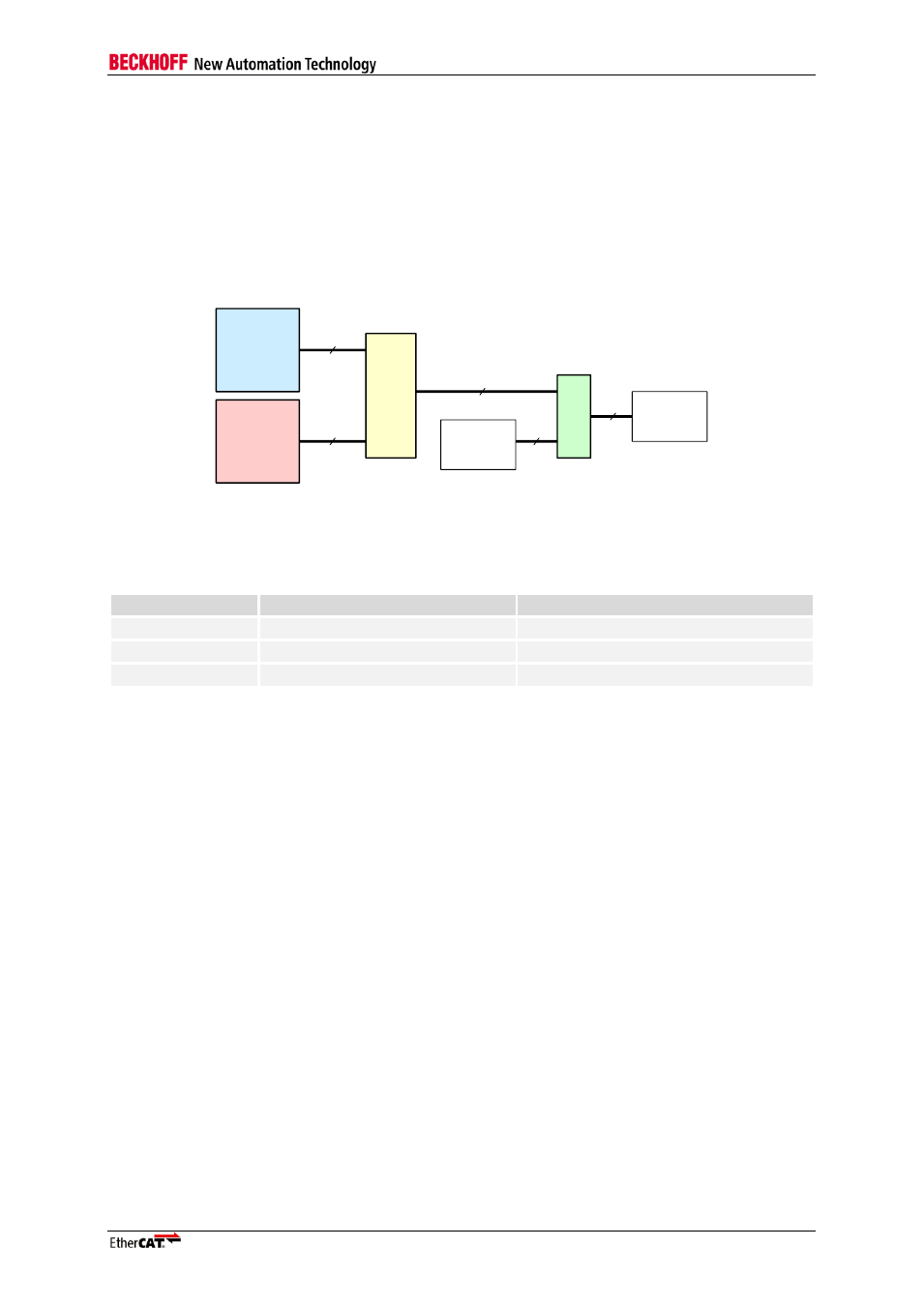

ECAT event requests are used to inform the EtherCAT master of slave events. ECAT events make

use of the IRQ field inside EtherCAT datagrams. The ECAT Event Request register (0x0210:0x0211)

is combined with the ECAT Event Mask register (0x0200:0x0201) using a logical AND operation. The

resulting interrupt bits are combined with the incoming ECAT IRQ field using a logical OR operation,

and written into the outgoing ECAT IRQ field. The ECAT Event Mask register allows for selecting the

interrupts which are relevant for the EtherCAT master and handled by the master application.

NOTE: The master cannot distinguish which slave (or even more than one) was the origin of an interrupt.

16

16

16

16

&

ECAT Event

Request

Register

(0x0210:0x0211)

ECAT Event

Mask

Register

(0x0200:0x0201)

16

≥1

Received

ECAT Event

Transmitted

ECAT Event

Figure 42: ECAT Interrupt Masking

Registers used for ECAT Interrupts are described in Table 48:

Table 48: Registers for ECAT Event Request Configuration

Register Address

Name

Description

0x0200:0x0201

ECAT Event Mask

Mask register

0x0210:0x0211

ECAT Event Request

Pending Interrupts

0x0804 + N*8

SyncManager Control

Mapping SyncManager Interrupts

NOTE: Some of these registers are not available in specific ESCs. Refer to Section II for details.

12.3 Clearing Interrupts Accidentally

Event request registers and register actions which clear interrupts are intended to be accessed

independently, i.e., with separate EtherCAT frames or separate PDI accesses. Otherwise it may

happen that interrupts and/or data are missed.

Examples:

Using SPI to read a SyncManager buffer: polling SyncManager buffers and interrupts delivered at

the beginning of each SPI access in the same access can lead to missed interrupts/data. Fault

scenario: the interrupt is not pending while the interrupts delivered at the beginning of the access

are sampled. The µController gets the information “no interrupt”, but it continues reading the

SyncManager buffer because the read command cannot be stopped without causing a PDI error.

If the SyncManager Interrupt occurs in the time windows between interrupt sampling and buffer

reading, new buffer data will be delivered and the interrupt is acknowledged. As a consequence,

the µController application will ignore the new data because no interrupt was set.

Solution: Read the SyncManager buffer only if the IRQ signal indicates a pending interrupt or if a

preceding access indicates pending interrupts.

Using a single ECAT frame to read DC Latch0/1 status and Latch Time registers: the status

registers may indicate no event, but if the event occurs in the time window between reading status

and time registers, the new latch time will be delivered and the corresponding interrupt is cleared

directly. The master gets the information “no interrupt”, but new latch times, so it will ignore the

time values and the interrupt/data is missed.

Solution: Read DC Latch time registers only if an ECAT event was indicated in a previous frame or

if the DC Latch status registers were polled in a previous frame.