2 esc to standard ethernet mac, Esc to standard ethernet mac, Standard ethernet mac (µc/fpga) – BECKHOFF EtherCAT Technology Section I User Manual

Page 54: 25 mhz

Ethernet Physical Layer

I-34

Slave Controller

– Technology

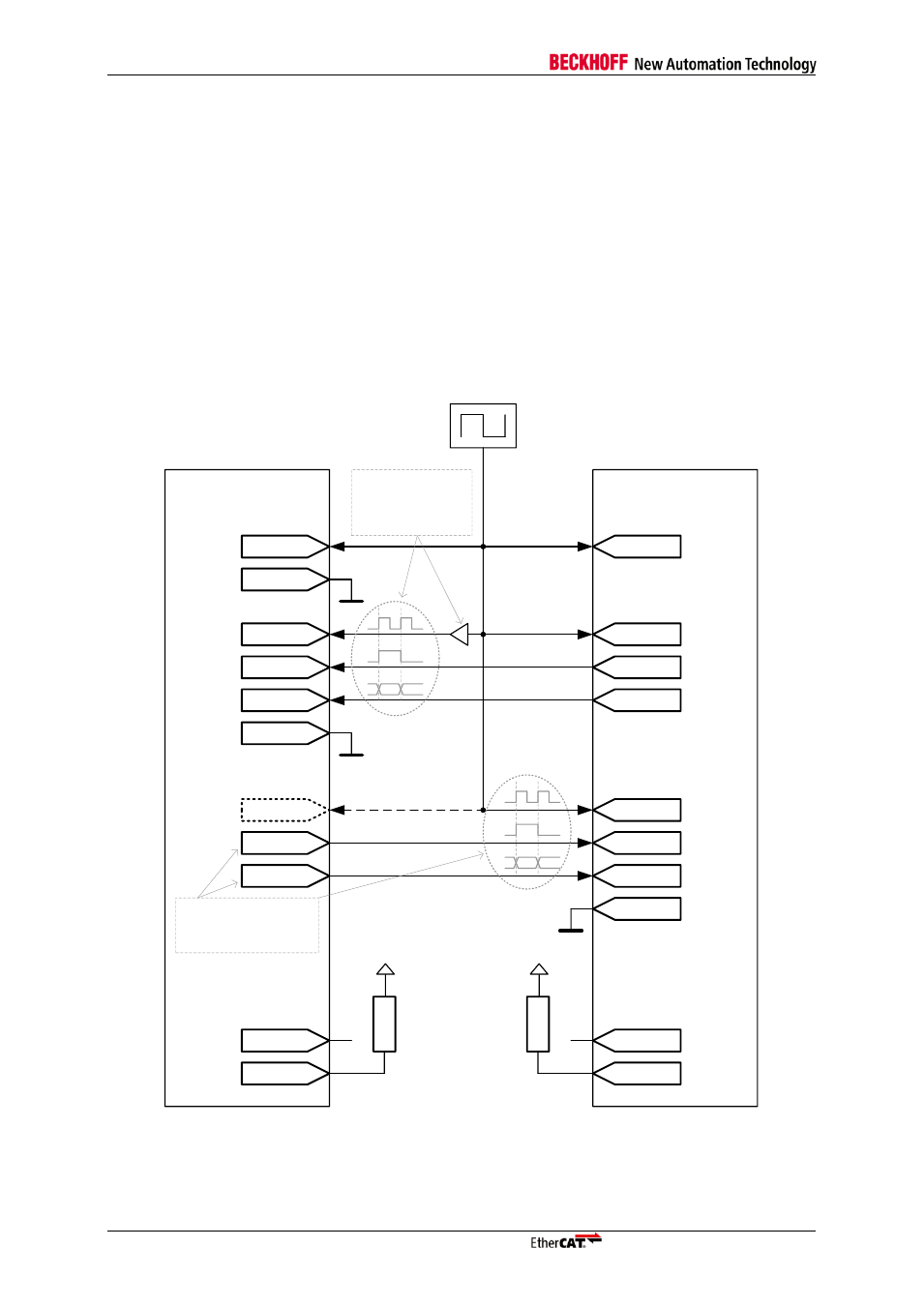

5.14.2 ESC to Standard Ethernet MAC

If an ESC is to be connected directly to a standard Ethernet MAC (e.g. µController or FPGA), RX

timing at the ESC and the MAC has to be checked. Since TX Shift configuration is not possible in the

MAC, RX_CLK for the ESC has to be adjusted (delayed) to achieve proper RX timing at the ESC.

An EtherCAT slave controller can be directly connected to a standard Ethernet MAC using MII as

shown in the figure below. The timing of RX_DV and RXD with respect to RX_CLK has to be checked

at both ESC and MAC to be compliant with the IEEE 802.3 requirements of min. 10 ns setup time and

min. 10 ns hold time. The timing can be adjusted by configuring the TX Shift setting of the ESC and

the clock buffer (e.g. using one or more buffers).

If the standard Ethernet MAC completely uses the IEEE 802.3 TX signal timing window of 0 to 25 ns,

standard compliant RX timing (-10..10 ns) is impossible. Since most Beckhoff ESCs do not require the

entire IEEE802.3 RX timing window (check in Section III), a valid configuration is possible even in this

case.

ESC

REF_CLK

LINK_MII*

RX_CLK

RX_DV

RXD[3:0]

TX_CLK

TX_EN

TXD[3:0]

RX_ER

MDC

MDIO

Standard Ethernet

MAC (µC/FPGA)

CLK_IN

RX_CLK

RX_DV

RXD[3:0]

TX_CLK

TX_EN

TXD[3:0]

RX_ER

MDC

MDIO

25 MHz

4

K

7

* if LINK_MII is act. low

V

CC I/O

4

K

7

V

CC I/O

Configure TX Shift and

check RX timing

(setup/hold>10 ns)

Add delay (e.g.

clock buffers) to

adjust RX timing

(setup/hold>10 ns)

Figure 15: Back-to-Back MII Connection (ESC and standard MAC)