2 pdi register function acknowledge by write, Pdi register function acknowledge by write – BECKHOFF EtherCAT Technology Section I User Manual

Page 112

Process Data Interface (PDI)

I-92

Slave Controller

– Technology

16.2 PDI register function acknowledge by write

Some ESC functions are triggered by writing or reading individual byte addresses, e.g., SyncManager

buffer change or AL event request acknowledge. With an increasing data bus width of the

µControllers, this can lead to restrictions or even problems.

Since most µControllers are using byte enable signals for write accesses, there is no restriction for

functions which are triggered by writes. But many µControllers are not using the byte enable signals

for read accesses, they expect to get a whole data bus width of read data. Reading individual bytes is

not possible. This can lead to problems especially by accidentally reading byte addresses which

trigger certain ESC functions. Consider a SyncManager buffer area from 0x1000-0x1005. A 32 bit

µController application might read the buffer byte-wise. The first access to 0x1000 would open the

buffer, and it would also read 0x1001-0x1003. The second access would read 0x1001, and also

0x1000/0x1002-0x1003. The problem occurs when address 0x1004 is to be read, because this would

also read 0x1005. The data of 0x1005 is discarded, but the buffer is closed. When the µC reads

0x1005, it will always get 0

– the data seems to be corrupted. A similar issue occurs for DC

SyncSignal acknowledging (registers 0x098E and 0x098F). A 32 bit µController would always

acknowledge SYNC0 and SYNC1 at the same time, it is not possible to acknowledge them separately.

This problem can be overcome by enabling PDI register function acknowledge by write. In this mode,

all functions which are originally triggered by read access are now triggered by corresponding write

accesses

– which use byte enables and thus can be restricted to certain bytes.

This feature is enabled by IP Core configuration. The current status has to be checked by the

µController application in PDI information register 0x014E[0], before using this function.

This feature affects reading of SyncManager buffers and reading of certain registers from PDI side.

There is no change to the EtherCAT master side at all. Refer to chapter 8 for SyncManager behavior.

The following registers are affected by the PDI register function acknowledge by write feature:

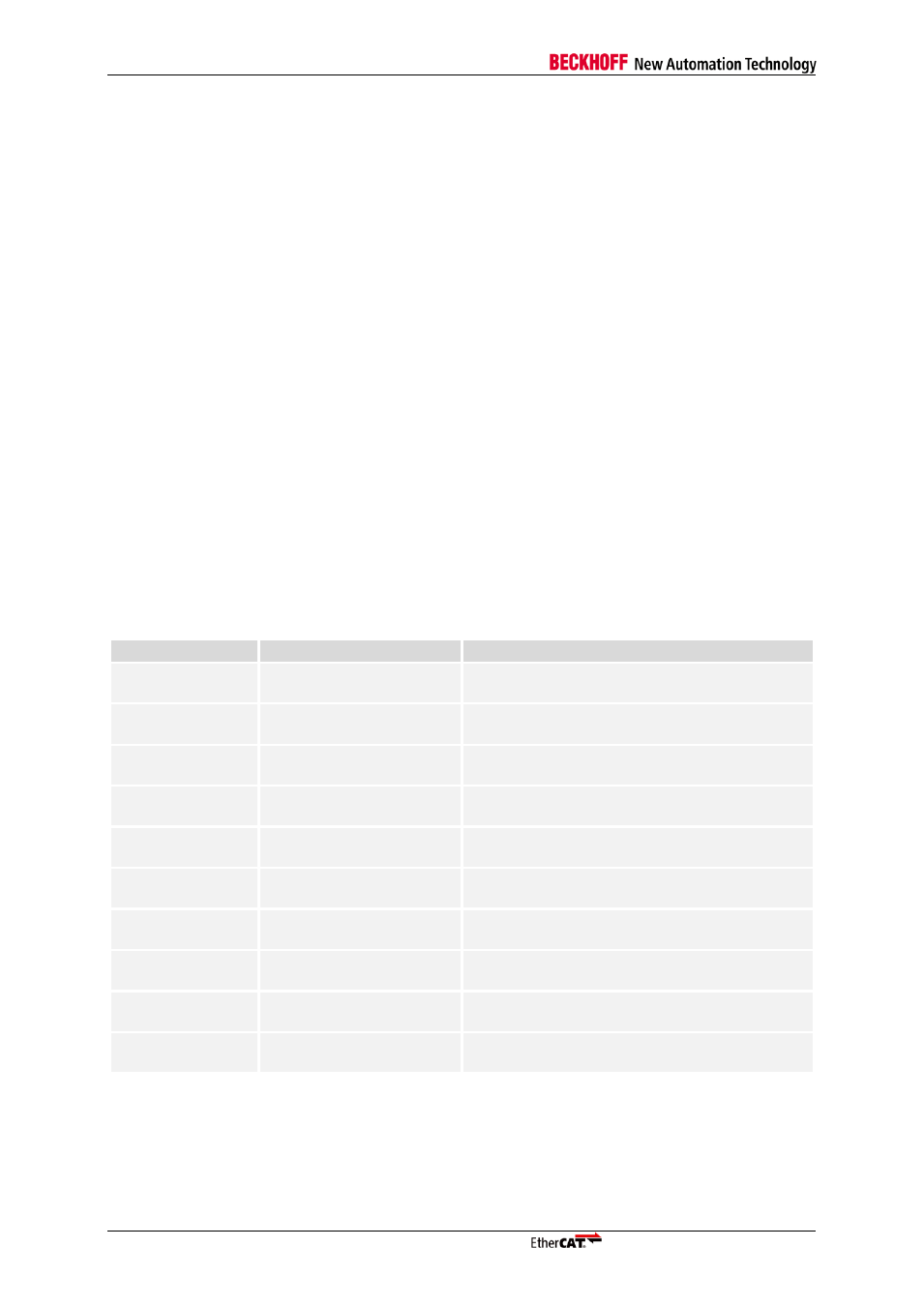

Table 58: Functions/registers affected by PDI register function acknowledge by write

Address

Name

Trigger function

any

SyncManager buffer end

address

Read SyncManager buffer, then write to buffer

end address to acknowledge buffer reading.

0x0120:0x0121

AL Control

Read 0x0120:0x0121 after AL Control changes,

then write to 0x0120 to acknowledge reading.

0x0440

Watchdog Status Process

Data

Read 0x0440, then write to 0x0440 to clear AL

event request 0x0220[6]

0x0806+y*16

SyncManager Activate

Read 0x0806+y*16, then write to 0x0806+y*16

to clear AL event request 0x0220[4]

0x098E

SYNC0 Status

Read 0x098E, then write to 0x098E to

acknowledge DC Sync0 Status 0x098E[0]

0x098F

SYNC1 Status

Read 0x098E, then write to 0x098E to

acknowledge DC Sync1 Status 0x098F[0]

0x09B0:0x09B7

Latch0 Time Positive Edge

Read 0x09B0:0x09B7, then write to 0x09B0 to

clear DC Latch0 Status 0x09AE[0]

0x09B8:0x09BF

Latch0 Time Negative

Edge

Read 0x09B8:0x09BF, then write to 0x09B8 to

clear DC Latch0 Status 0x09AE[1]

0x09C0:0x09C7

Latch1 Time Positive Edge

Read 0x09C0:0x09C7, then write to 0x09C0 to

clear DC Latch1 Status 0x09AF[0]

0x09C8:0x09CF

Latch1 Time Negative

Edge

Read 0x09C8:0x09CF, then write to 0x09C8 to

clear DC Latch1 Status 0x09AF[1]