4 resetting the time control loop, 5 drift compensation, Resetting the time control loop – BECKHOFF EtherCAT Technology Section I User Manual

Page 76: Drift compensation

Distributed Clocks

I-56

Slave Controller

– Technology

9.1.4

Resetting the Time Control Loop

Before starting drift compensation, the internal filters of the Time Control Loop must be reset. Their

current status is typically unknown, and they can have negative impact on the settling time. The filters

are reset by writing the Speed Counter Start value to the Speed Counter Start register

(0x0930:0x0931). Writing the current value of the register again is sufficient to reset the filters.

Registers used for resetting the Time Control Loop filters are listed in Table 27.

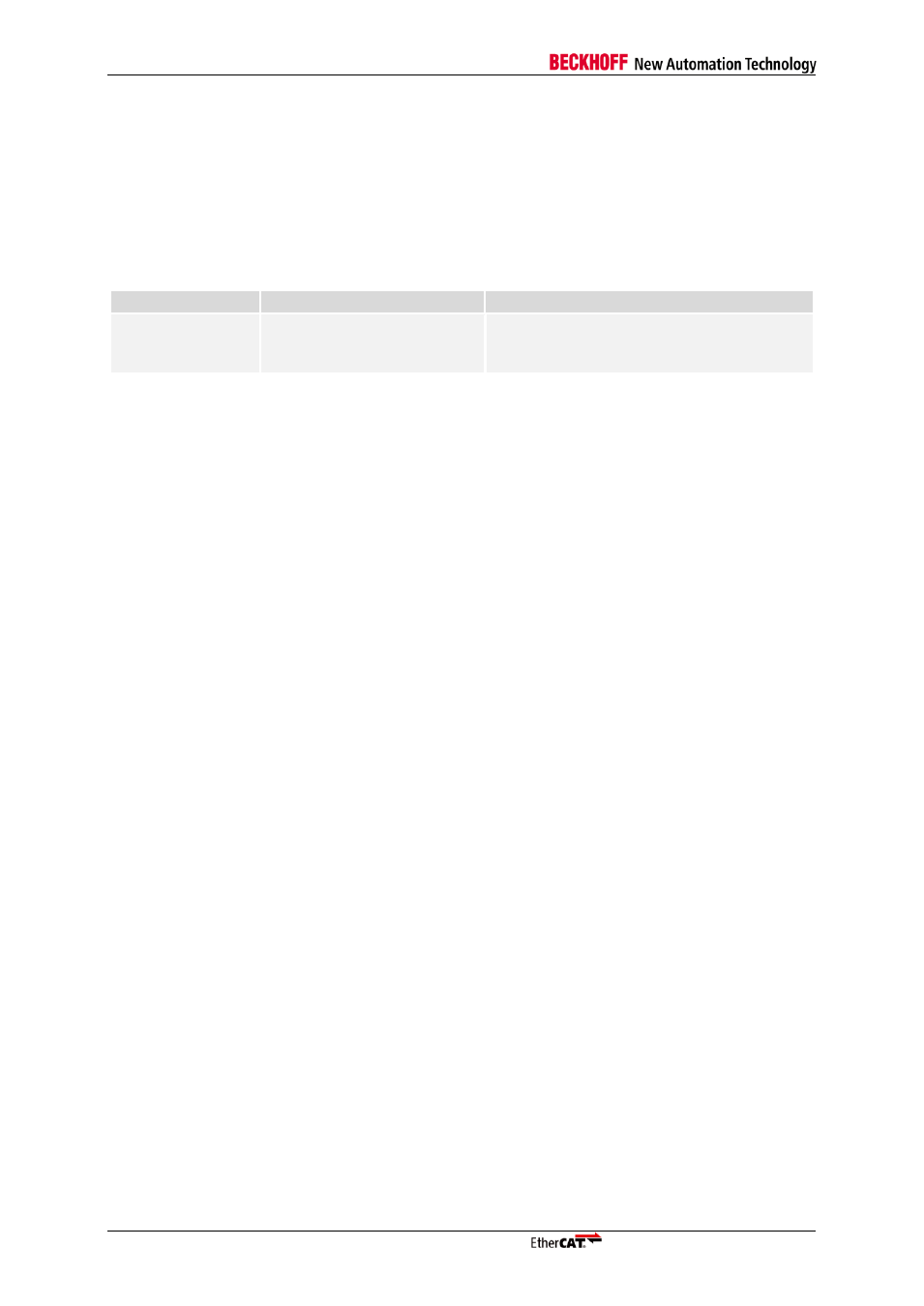

Table 28: Registers for Resetting the Time Control Loop

Register Address

Name

Description

0x0930:0x0931

Speed Counter Start

Bandwidth for adjustment of local copy of

System Time

Writing a value resets the internal filters.

9.1.5

Drift Compensation

After the delay time between the Reference Clock and the slave clocks has been measured, and the

offset between both clocks has been compensated, the natural drift of every local clock (emerging

from quartz variations between the

Reference Clock’s quartz and the local quartz) is compensated by

the time control loop which is integrated into each ESC.

For drift compensation, the master distributes the System Time from the Reference Clock to all slave

clocks periodically. The ARMW or FRMW commands can be used for this purpose. The time control

loop of each slave takes the lower 32 bit of the System Time received from the Reference Clock and

compares it to its local copy of the System Time. For this difference, the propagation delay has to be

taken into account:

Δt = (t

Local time

+ t

Offset

– t

Propagation delay

)

– t

Received System Time

If

Δt is positive, the local time is running faster than the System time, and has to be slowed down. If Δt

is negative, the local time is running slower than the System time, and has to be sped up. The time

control loop adjusts the speed of the local clock.

For a fast compensation of the static deviations of the clock speeds, the master should initially send

many ARMW/FRMW commands (e.g. 15,000) for drift compensation in separate frames after

initialization of the propagation delays and offsets. The control loops compensate the static deviations

and the distributed clocks are synchronized. Afterwards, the drift compensation frames are sent

periodically for compensation of dynamic clock drifts.

NOTE: The System Time Offset allows fast compensation of differences between local copy of the system time

and the System Time, the drift compensation is very slow. Thus, shortly before drift compensation is started, the

offset should be roughly compensated using the System Time Offset register. Otherwise settling time might

become very high.

NOTE:

Δt must not exceed 2

30

ns (~ 1 second), otherwise stability is not guaranteed. For fast settling times,

Δt

should be as low as possible.

Time Control Loop Configuration and Status

The time control loop has some configuration and status registers (System Time Difference, Speed

Counter Start, Speed Counter Difference, System Time Difference Filter Depth, and Speed Counter

Filter Depth). The default settings of these registers are sufficient for proper operation of the drift

compensation. Setting the Speed Counter Filter Depth (0x0935) to 0 improves control loop behavior.

The System Time Difference register (0x092C:0x092F) contains the mean value of the difference

between local copy of the System Time and the System Time (

Δt). This value converges to zero when

both times are identical.

The Speed Counter Start register (0x0930:0x0931) represents the bandwidth of the drift

compensation. The value of the Speed Counter Difference register (0x0932:0x0933) represents the

deviation between the clock periods of the Reference Clock and the local ESC.