BECKHOFF EtherCAT Technology Section I User Manual

Page 4

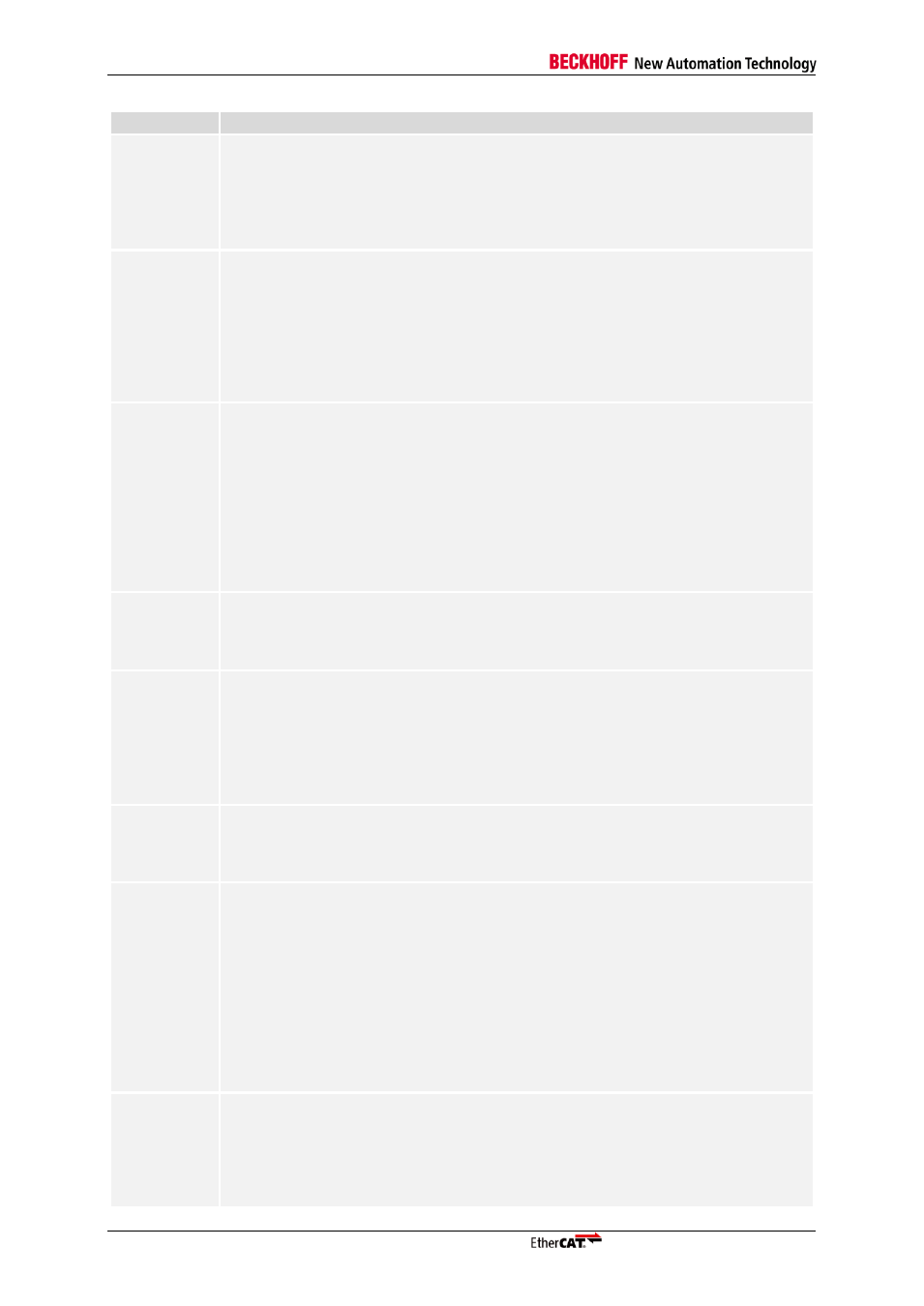

DOCUMENT HISTORY

I-IV

Slave Controller

– Technology

Version

Comment

1.5

EEPROM Read/Write/Reload example: corrected register addresses

Updated/clarified PHY requirements, PHY link loss reaction time is mandatory

Enhanced Link Detection can be configured port-wise depending on ESC

Added DC Activation and DC Activation State features for some ESCs

ESC10 removed

Editorial changes

1.6

Fill reserved EEPROM words of the ESC Configuration Area with 0

Interrupt chapter: example for proper interrupt handling added

Use Position Addressing only for bus scanning at startup and to detect newly

attached devices

System Time PDI controlled: detailed description added

Added MII back-to-back connection example

Renamed Err(x) LED to PERR(x)

Editorial changes

1.7

Link status description enhanced

Clarifications for DC System Time and reference between clocks and registers

Chapter on avoiding unconnected Port 0 configurations added

Direct ESC to standard Ethernet MAC MII connection added

MI link detection and configuration must not be used without LINK_MII signals

Added criteria for detecting when DC synchronization is established

SII EEPROM interface is a point-to-point connection

PHY requirements: PHY startup should not rely on MDC clocking, ESD

tolerance and baseline wander compensation recommendations added

Editorial changes

1.8

Update to EtherCAT IP Core Release 2.3.0/2.03a

EEPROM acknowledge error (0x0502[13]) can also occur for a read access

ERR and STATE LED updated

Editorial changes

1.9

EtherCAT state machine: additional AL status codes defined

EtherCAT protocol: LRD/LRW read data depends on bit mask

Updated EBUS Enhanced Link Detection

Updated FMMU description

Loop control description updated

EtherCAT frame format (VLAN tag) description enhanced

Update to EtherCAT IP Core Release 2.3.2/2.03c

2.0

Update to EtherCAT IP Core Release 2.4.0/2.04a

SII/ESI denotation now consistent with ETG

Updated AL Status codes

Editorial changes

2.1

Update to EtherCAT IP Core Release 3.0.0/3.00a

Update to ET1100-0003 and ET1200-0003

RUN/ERR LED description enhanced

Added RGMII and FX operation

Added Gigabit Ethernet PHY chapter

Updated FIFO size configuration (default from SII)

Updated PHY address configuration

Added PDI register function acknowledge by write

Added propagation delay measurement in reverse mode (especially ET1200)

Enhanced ERR_LED description

Editorial changes

2.2

Update to EtherCAT IP Core Release 3.0.6/3.00g

Added resetting Distributed Clocks Time Loop Control filters to the

synchronization steps

Extended Back-to-Back MII connection schematic

Clarified EBUS standard link detection restrictions

Editorial changes