17 additional information, 1 esc clock source, 2 power-on sequence – BECKHOFF EtherCAT Technology Section I User Manual

Page 114: Additional information, Esc clock source, Power-on sequence, Table 59: esc power-on sequence

Additional Information

I-94

Slave Controller

– Technology

17 Additional Information

17.1 ESC Clock Source

The initial accuracy of the ESC clock sources has to be 25 ppm or better. This enables FIFO size

reduction, i.e., forwarding delay reduction, and supports fast DC locking. Existing designs do not need

to be changed.

17.2 Power-on Sequence

The power-on sequence of ESCs looks like this:

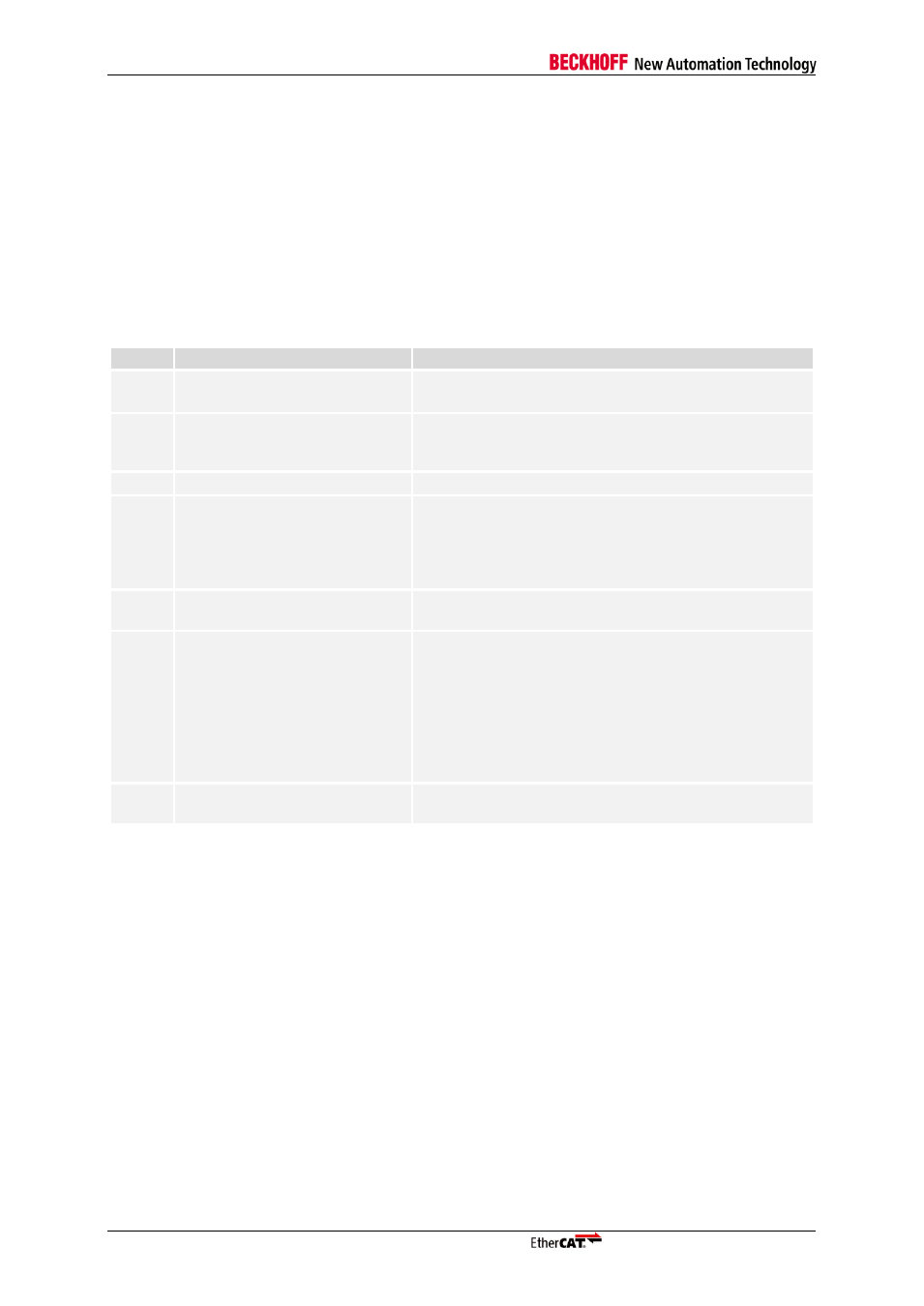

Table 59: ESC Power-On Sequence

No.

Step

Result

1

Power-on

Voltages reach proper levels

ASICs only: Power-on values are sampled

2

(FPGA

only)

Loading FPGA configuration

FPGA loads its hardware configuration

3

PLL locks

Clocks are generated properly

4

Release RESET

ESC operation begins. Process memory is not

accessible until the SII EEPROM is loaded, as well as

any function depending on ESC Configuration data. IP

Core: PDI is operational; others: PDI is not operational

until EEPROM is loaded.

5*

Links are established

EtherCAT communication begins, master can access

ESC registers

6*

Loading ESC EEPROM

Only upon successful EEPROM loading:

ESC Configuration registers initialized

PDI is activated (not IP Core: active after RESET)

PDI operation begins

Register bit 0x0110[0] turns to 1

Process Data RAM becomes accessible

Some PDIs: EEPROM_Loaded signal is driven high

ESC is in Init state

7

Example: Master proceeds to

Operational state

ESC proceeds to Operational state

* Steps 5 and 6 are executed in parallel.

NOTE: The PDI signals are not driven until the ESC EEPROM is loaded successfully, especially the

EEPROM_Loaded signal is not driven and needs a pull-down resistor if it is used.