Altera Stratix V Avalon-ST User Manual

Page 101

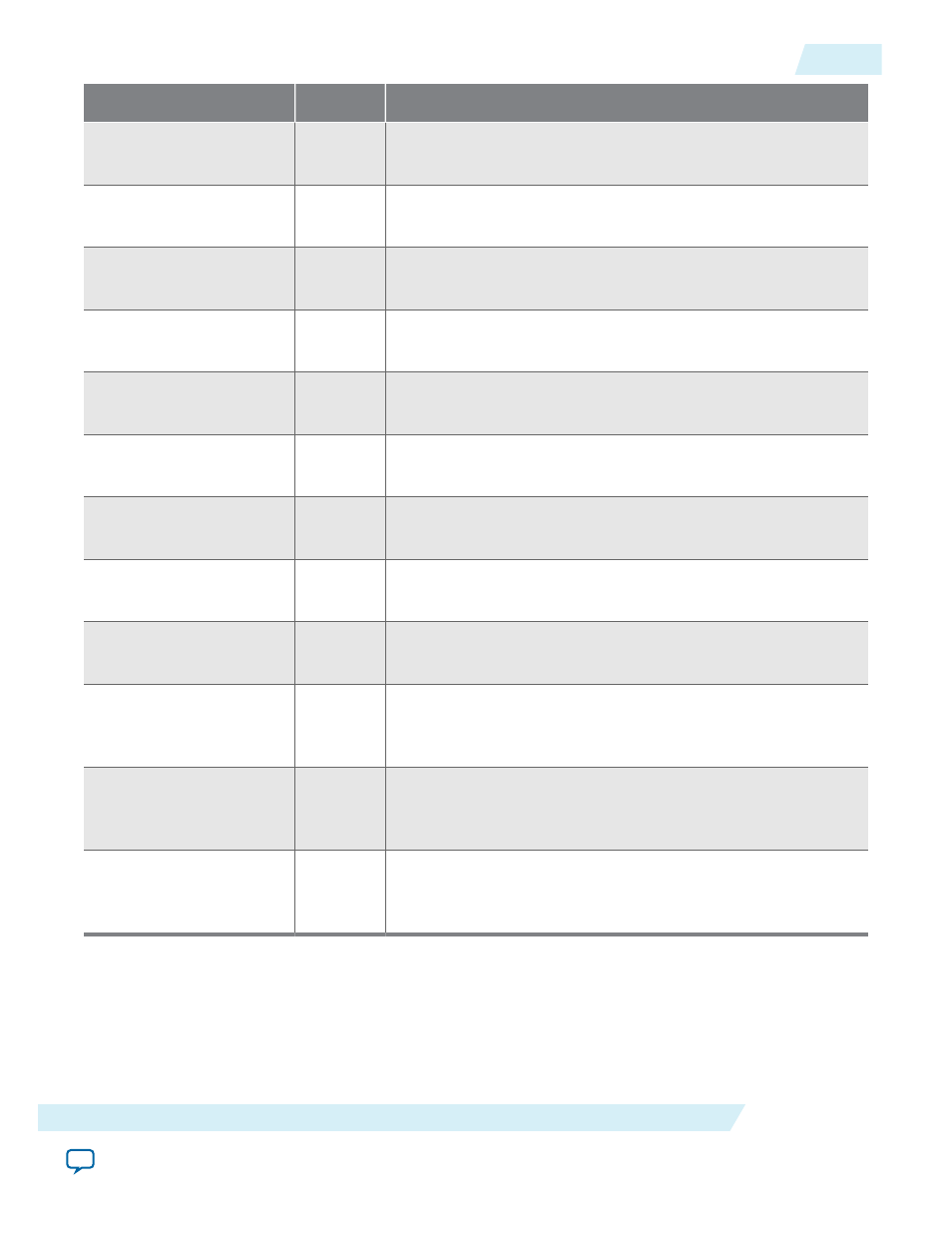

Signal Name

Direction

Description

err_tlmalf

Output

When asserted, indicates a malformed TLP was detected and

dropped. This is a real-time active high pulse.

err_surpdwn_dll

Output

When asserted, indicates a surprise down error occurred. This is

a real-time active high pulse.

err_dllrcv

Output

When asserted, indicates a Data Link Protocol Error. This is a

real-time active high pulse.

err_dll_repnum

Output

When asserted, indicates a Replay_NUM rollover. This is a

real-time active high pulse.

err_dllreptim

Output

When asserted, indicates a Replay Timer Timeout. This is a

real-time active high pulse.

err_dllp_baddllp

Output

When asserted, indicates a bad DLLP was detected. This is a

real-time active high pulse.

err_dll_badtlp

Output

When asserted, indicates a bad TLP was detected. This is a

real-time active high pulse.

err_phy_tng

Output

When asserted, indicates a Link Training Error. This is a

real-time active high pulse.

err_phy_rcv

Output

When asserted, indicates a Receiver Error. This is a real-time

active high pulse.

root_err_reg_sts

Output

When asserted, indicates a a bit in the Root Error Status Register

is set. The Application Layer can read this register using the LMI.

This bit clears when read.

corr_err_reg_sts

Output

When set to 1, indicates that a bit in Correctable Error Status

Register is set. The Application Layer can read this register using

the LMI. This bit clears when read.

unc_err_reg_sts

Output

When set to 1, indicates that a bit in Uncorrectable Error Status

Register is set. The Application Layer can read this register using

the LMI. This bit clears when read.

Related Information

Configuration Space Bypass Mode

on page 10-7

UG-01097_avst

2014.12.15

Configuration Space Bypass Mode Interface Signals

5-49

Interfaces and Signal Descriptions

Altera Corporation