Altera Stratix V Avalon-ST User Manual

Page 99

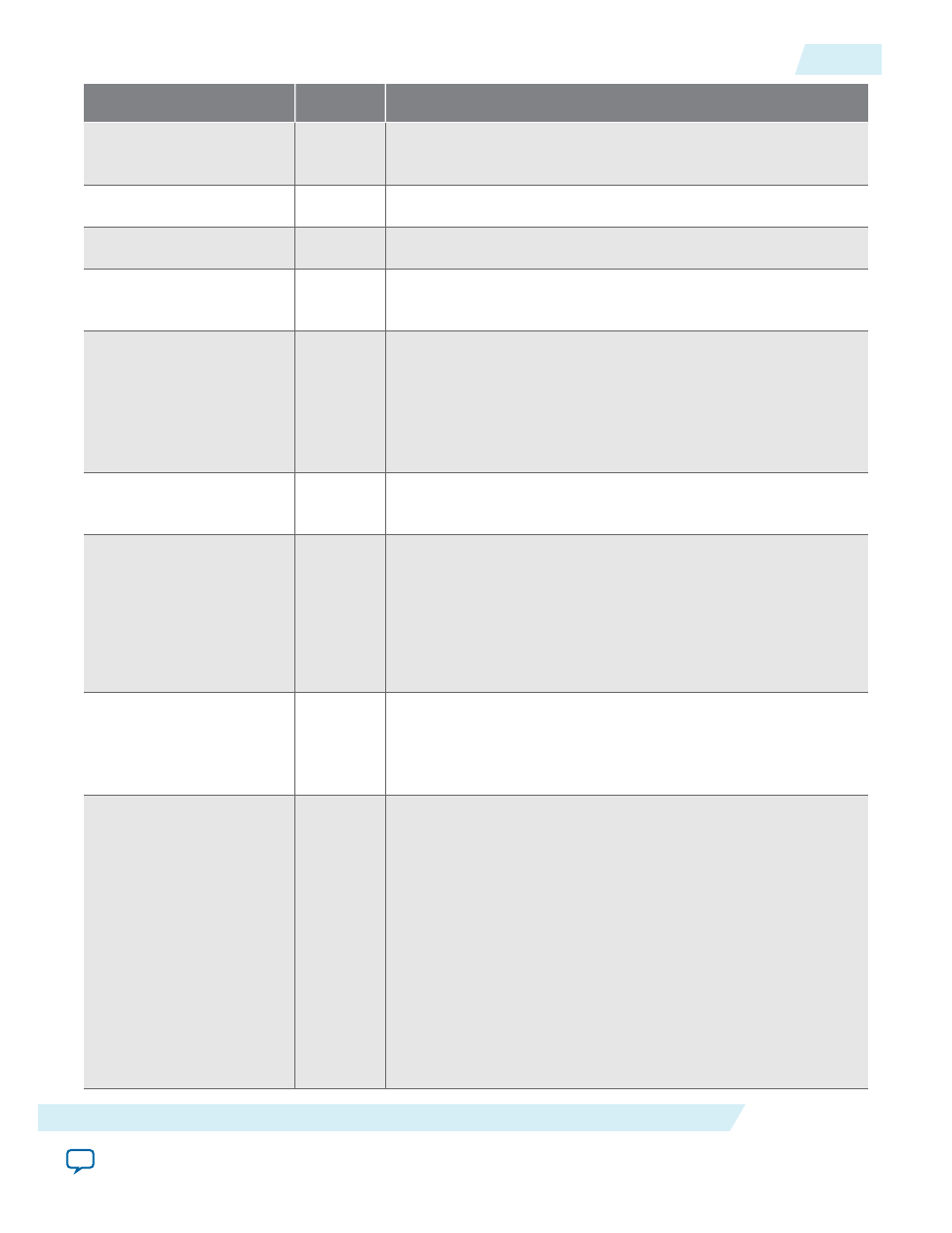

Signal Name

Direction

Description

link_train

Output

Reported as Bit 10 of the

Link Status Register

. When

asserted, indicates that the link is training.

l0state

Output

When asserted, indicates that the LTSSM is in the L0 state.

l0sstate

Output

When asserted, indicates that the LTSSM is in L0 or L0s state.

rx_val_pm[0]

Output

When asserted, indicates the Configuration Space has received a

Power Management DLLP.

rx_typ_pm[2:0]

Output

Signals the type of received PM DLLP. Has the following values:

• 000b: PM_Enter_L1

• 001b: PM_Enter_L2L3

• 011b: PM_AS_Request_L1

• 100b: PM_Request_Ack

tx_ack_pm

Output

Pulse. Ack from TX Data Link in response to Power

Management DLLP request

tx_req_pm_pld

.

ack_phypm[1:0]

Output

Acknowledge of transition to and from the low-power state when

operations have been completed. The acknowledge bit mapping

is the same as the request bit mapping.

• Bit 0:

rxelecidle

deasserted or Training Sequence 1 (TS1)

received, or

rxvalid

deasserted. Used for L1 exit.

• Bit 1: RX Electrical Idle Ordered Set detected or TS1 received.

vc_status[0]

Output

When asserted, indicates that VC0 credits are initialized. When

asserted, the

VC Negotiation Pending

bit of the

VC Resource

Status Register

can be cleared indicating that negotiation is

complete.

rxfc_max

Output

When asserted, indicates the Transaction Layer has no high

priority FC updates to send. High priority updates occur under

the following conditions:

1. The FC update timer expires because no new credits have

become available in the timeout period since last update.

2. The source has used all header credits from the last FC update

and header credits have freed up.

3. The last FC update did not give the source enough data

credits to send a maximum payload TLP and data credits have

since freed up.

Detects when TLP processing is complete for entry into low

power state.

UG-01097_avst

2014.12.15

Configuration Space Bypass Mode Interface Signals

5-47

Interfaces and Signal Descriptions

Altera Corporation