Altera Stratix V Avalon-ST User Manual

Page 273

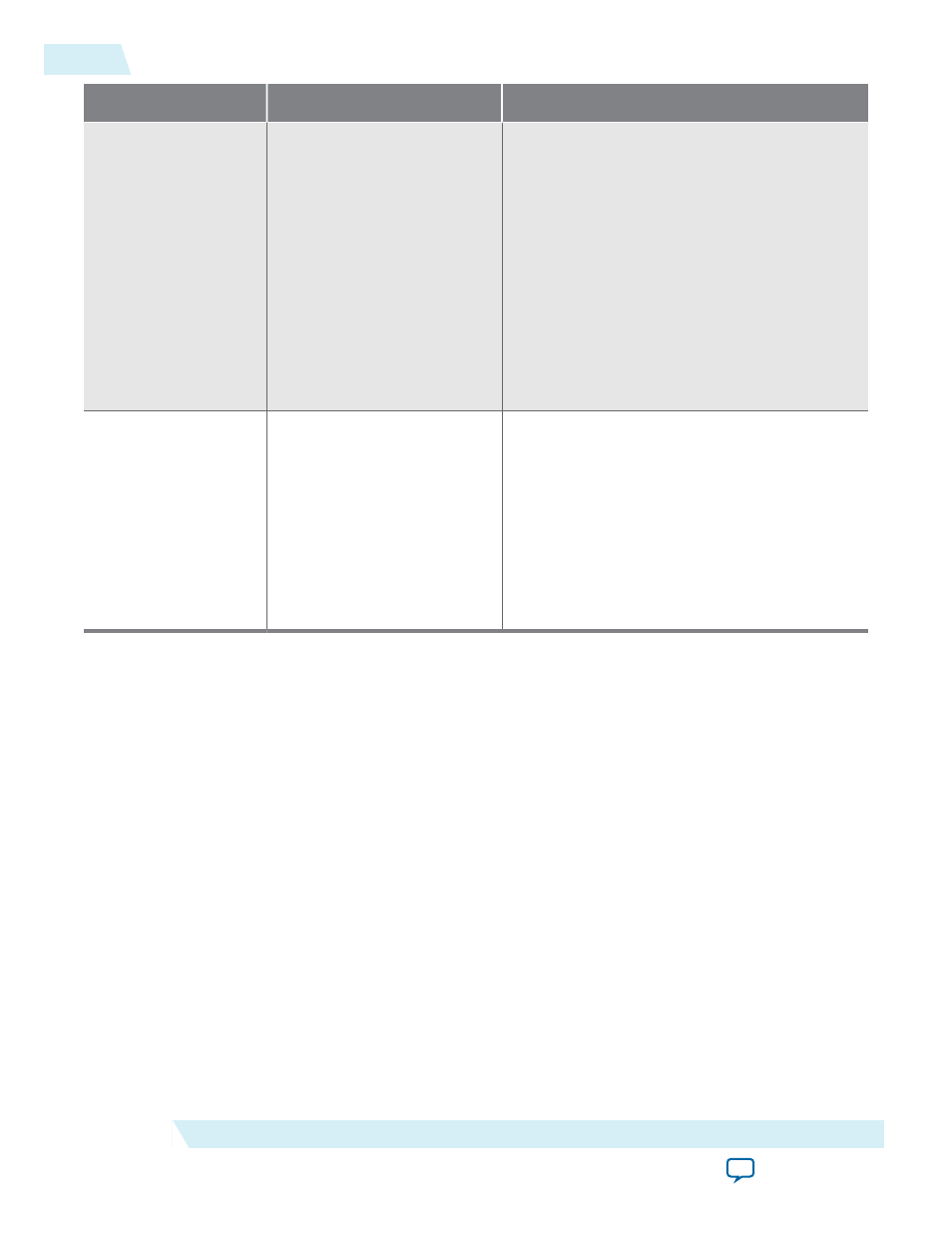

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions

Link fails due to

unstable

rx_

signaldetect

Confirm that

rx_signaldetect

bus of the active lanes is all 1’s.

If all active lanes are driving all

1’s, the LTSSM state machine

toggles between Detect.Quiet(0),

Detect.Active(1), and

Polling.Active(2) states.

This issue may be caused by mismatches

between the expected power supply to RX side

of the receiver and the actual voltage supplied to

the FPGA from your boards. If your PCB drives

VCCT/VCCR with 1.0 V, you must apply the

following command to both P and N pins of

each active channel to override the default

setting of 0.85 V.

set_instance_assignment -name XCVR_

VCCR_VCCT_VOLTAGE 1_0V –to “pin”

Substitute the pin names from your design for

“pin”

.

Link fails because the

LTSSM state machine

enters Compliance

Confirm that the LTSSM state

machine is in

Polling.Compliance(3) using

SignalTap II.

Possible causes include the following:

• Setting

test_in[6]

=1 forces entry to

Compliance mode when a timeout is reached

in the Polling.Active state.

• Differential pairs are incorrectly connected

to the pins of the device. For example, the

Endpoint’s TX signals are connected to the

RX pins and the Endpoint’s RX signals are to

the TX pins.

Debugging Link Failure in L0 Due To Deassertion of tx_st_ready

There are many reasons that link may stop transmitting data. The following table lists some possible

causes.

18-4

Debugging Link Failure in L0 Due To Deassertion of tx_st_ready

UG-01097_avst

2014.12.15

Altera Corporation

Debugging