Lmi signals, Hard ip for pcie – Altera Stratix V Avalon-ST User Manual

Page 103

Signal Name

Direction

Description

cfg_par_err

Output

When asserted for a single cycle, indicates that a parity error was

detected in a TLP that was routed to internal Configuration

Space or to the Configuration Space Shadow Extension Bus. This

error is logged as an uncorrectable internal error in the VSEC

registers. For more information, refer to Uncorrectable Internal

Error Status Register. If this error occurs, you must reset the core

because parity errors can put the Hard IP in an unknown state.

cfg_par_err

Output

Indicates that a parity error in a TLP routed to the internal

Configuration Space or to the Configuration Space Shadow

Extension Bus. This error is also logged in the Vendor Specific

Extended Capability internal error register. You must reset the

Hard IP if this event occurs.

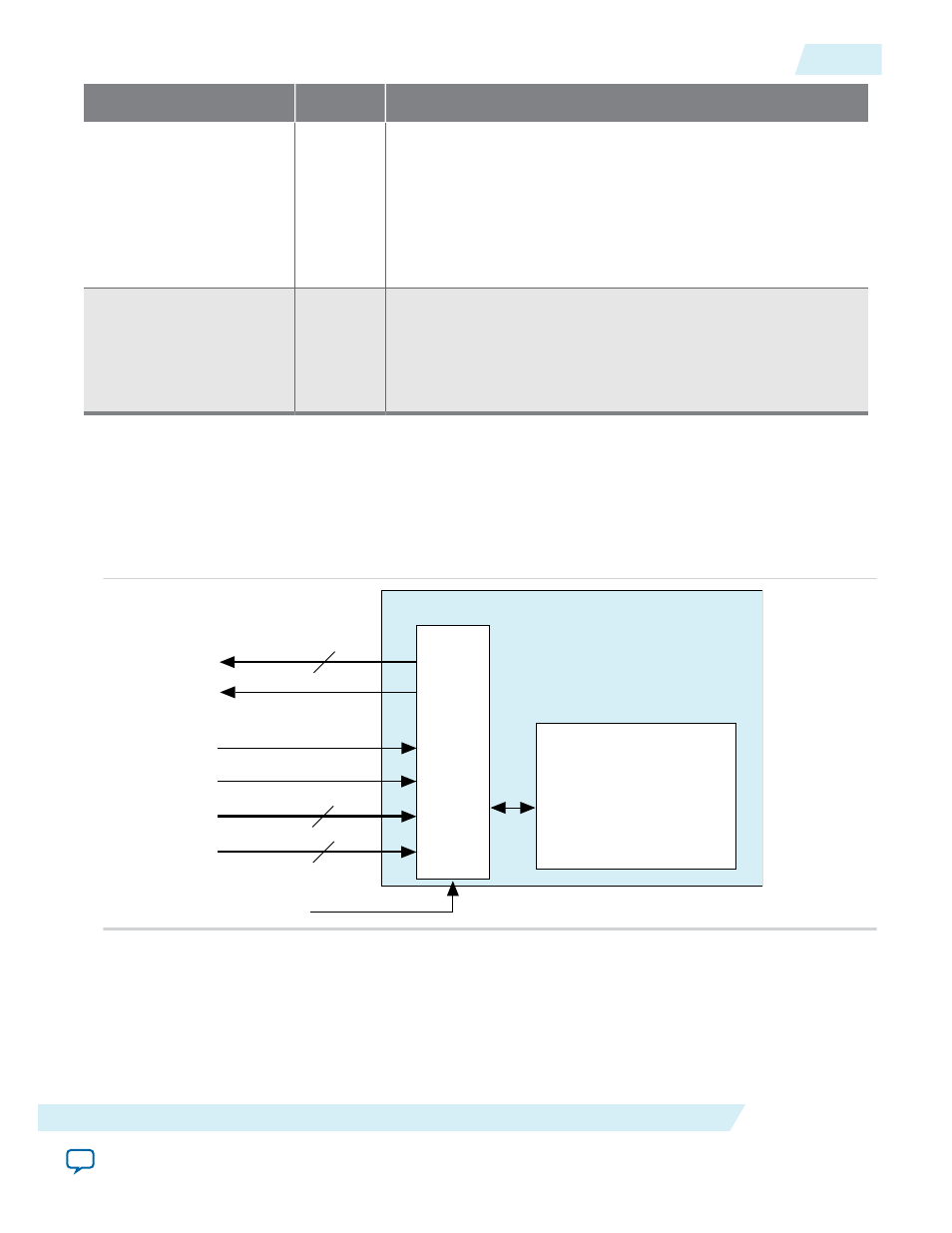

LMI Signals

LMI interface is used to write log error descriptor information in the TLP header log registers. The LMI

access to other registers is intended for debugging, not normal operation.

Figure 5-35: Local Management Interface

Configuration Space

128 32-bit registers

(4 KBytes)

LMI

32

lmi_dout

lmi_ack

15

lmi_addr

32

lmi_din

lmi_rden

lmi_wren

pld_clk

Hard IP for PCIe

The LMI interface is synchronized to

pld_clk

and runs at frequencies up to 250 MHz. The LMI address is

the same as the Configuration Space address. The read and write data are always 32 bits. The LMI

interface provides the same access to Configuration Space registers as Configuration TLP requests.

Register bits have the same attributes, (read only, read/write, and so on) for accesses from the LMI

interface and from Configuration TLP requests.

UG-01097_avst

2014.12.15

LMI Signals

5-51

Interfaces and Signal Descriptions

Altera Corporation