Hard ip for pci express – Altera Stratix V Avalon-ST User Manual

Page 169

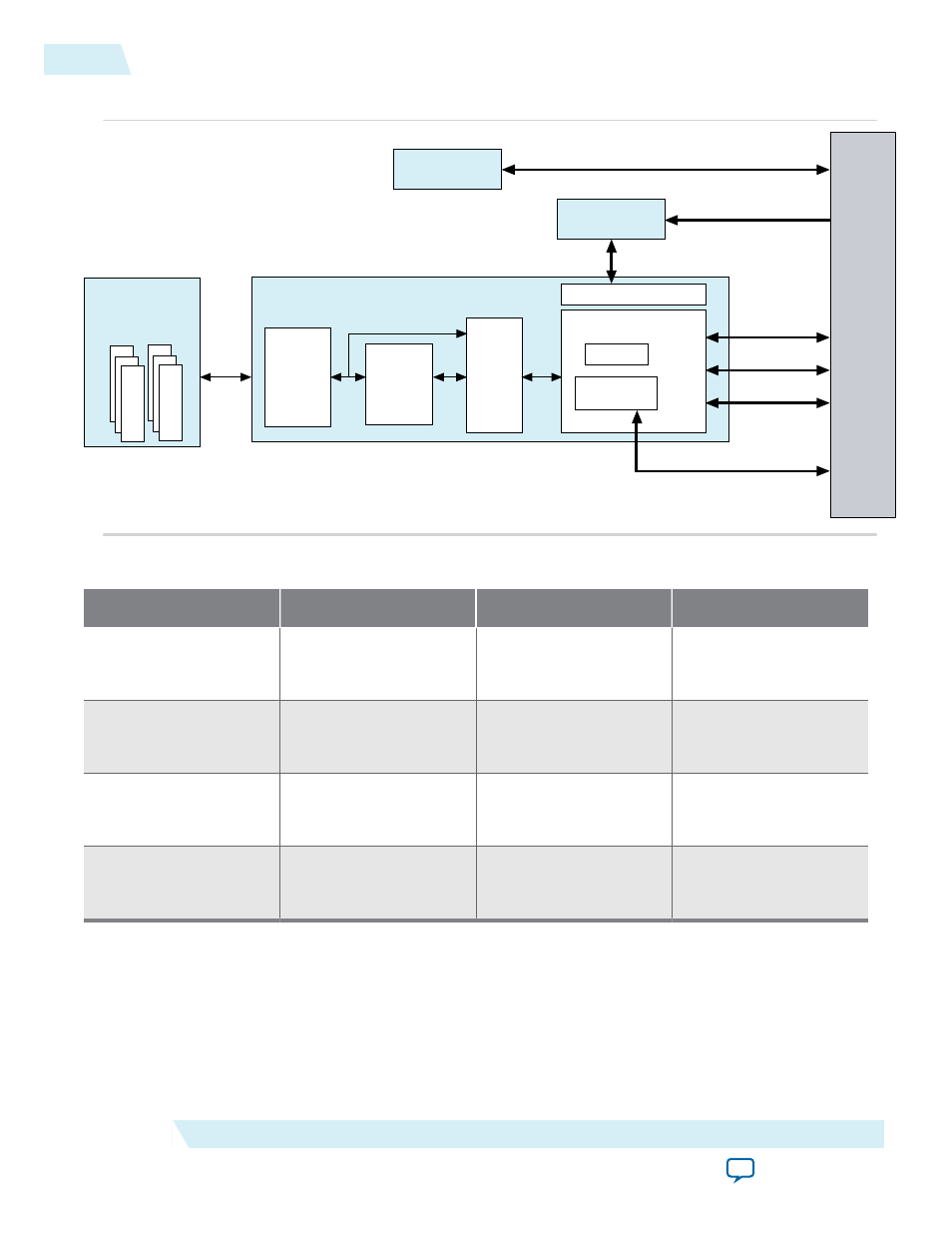

Figure 10-1: Stratix V Hard IP for PCI Express Using the Avalon-ST Interface

Clock

Domain

Crossing

(CDC)

Data

Link

Layer

(DLL)

Transaction Layer (TL)

PHYMAC

Hard IP for PCI Express

Avalon-ST TX

Avalon-ST RX

Side Band

Local

Management

Interface (LMI)

&

Reconfiguration

PIPE

Application

Layer

Clock & Reset

Selection

Configuration

Block

Configuration

Space

PCS

PMA

Physical Layer

(Transceivers)

Configuration via PCIe Link

RX Buffer

PHY IP Core for

PCI Express (PIPE)

Table 10-1: Application Layer Clock Frequencies

Lanes

Gen1

Gen2

Gen3

×1

125 MHz @ 64 bits or

62.5 MHz @ 64 bits

125 MHz @ 64 bits

125 MHz @64 bits

×2

125 MHz @ 64 bits

125 MHz @ 128 bits

250 MHz @ 64 bits or

125 MHz @ 128 bits

×4

125 MHz @ 64 bits

250 MHz @ 64 bits or

125 MHz @ 128 bits

250 MHz @ 128 bits or

125 MHz @ 256 bits

×8

250 MHz @ 64 bits or

125 MHz @ 128 bits

250 MHz @ 128 bits or

125 MHz @ 256 bits

250 MHz @ 256 bits

10-2

IP Core Architecture

UG-01097_avst

2014.08.18

Altera Corporation

IP Core Architecture