Single packet per cycle – Altera Stratix V Avalon-ST User Manual

Page 67

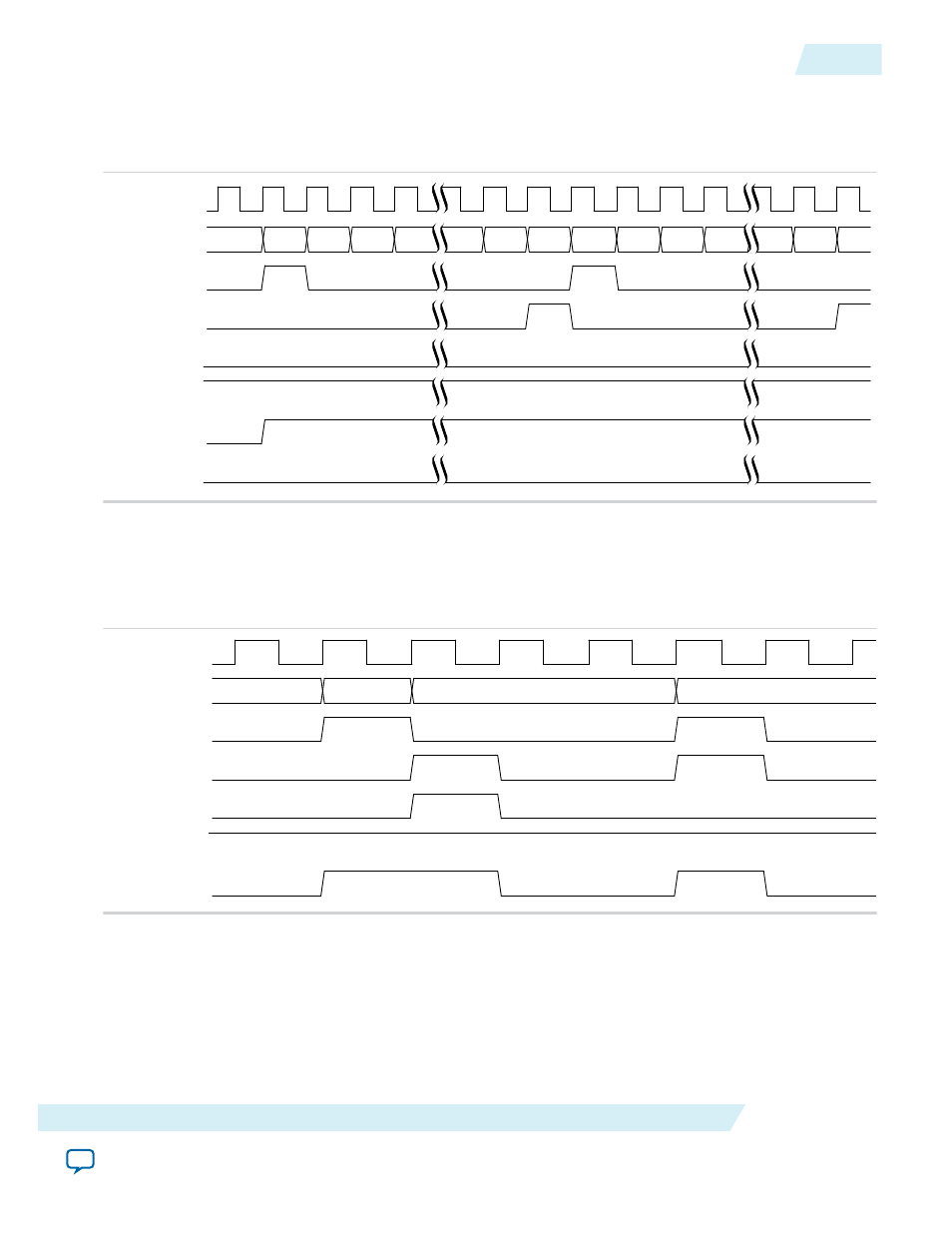

Figure 5-14: 128-Bit Avalon-ST Interface Back-to-Back Transmission

The following figure illustrates back-to-back transmission on the 128-bit Avalon-ST RX interface with no

idle cycles between the assertion of

rx_st_eop

and

rx_st_sop

.

pld_clk

rx_st_data[127:0]

rx_st_sop

rx_st_eop

rx_st_empty

rx_st_ready

rx_st_valid

rx_st_err

BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ...

...

BB

Figure 5-15: 128-Bit Packet Examples of rx_st_empty and Single-Cycle Packet

The following figure illustrates a two-cycle packet with valid data in the lower qword

(

rx_st_data[63:0]

) and a one-cycle packet where the

rx_st_sop

and

rx_st_eop

occur in the same

cycle.

pld_clk

rx_st_data[127:0]

rx_st_sop

rx_st_eop

rx_st_empty

rx_st_ready

rx_st_valid

0000090

1C0020000F0000000100004

450AC89000012FE0D10004

For a complete description of the TLP packet header formats, refer to Appendix A, Transaction Layer

Packet (TLP) Header Formats.

Single Packet Per Cycle

In single packer per cycle mode, all received TLPs start at the lower 128-bit boundary on a 256-bit

Avalon-ST interface. Turn on Enable Multiple Packets per Cycle on the System Settings tab of the

parameter editor to change multiple packets per cycle.

UG-01097_avst

2014.12.15

Single Packet Per Cycle

5-15

Interfaces and Signal Descriptions

Altera Corporation