Altera Stratix V Avalon-ST User Manual

Page 287

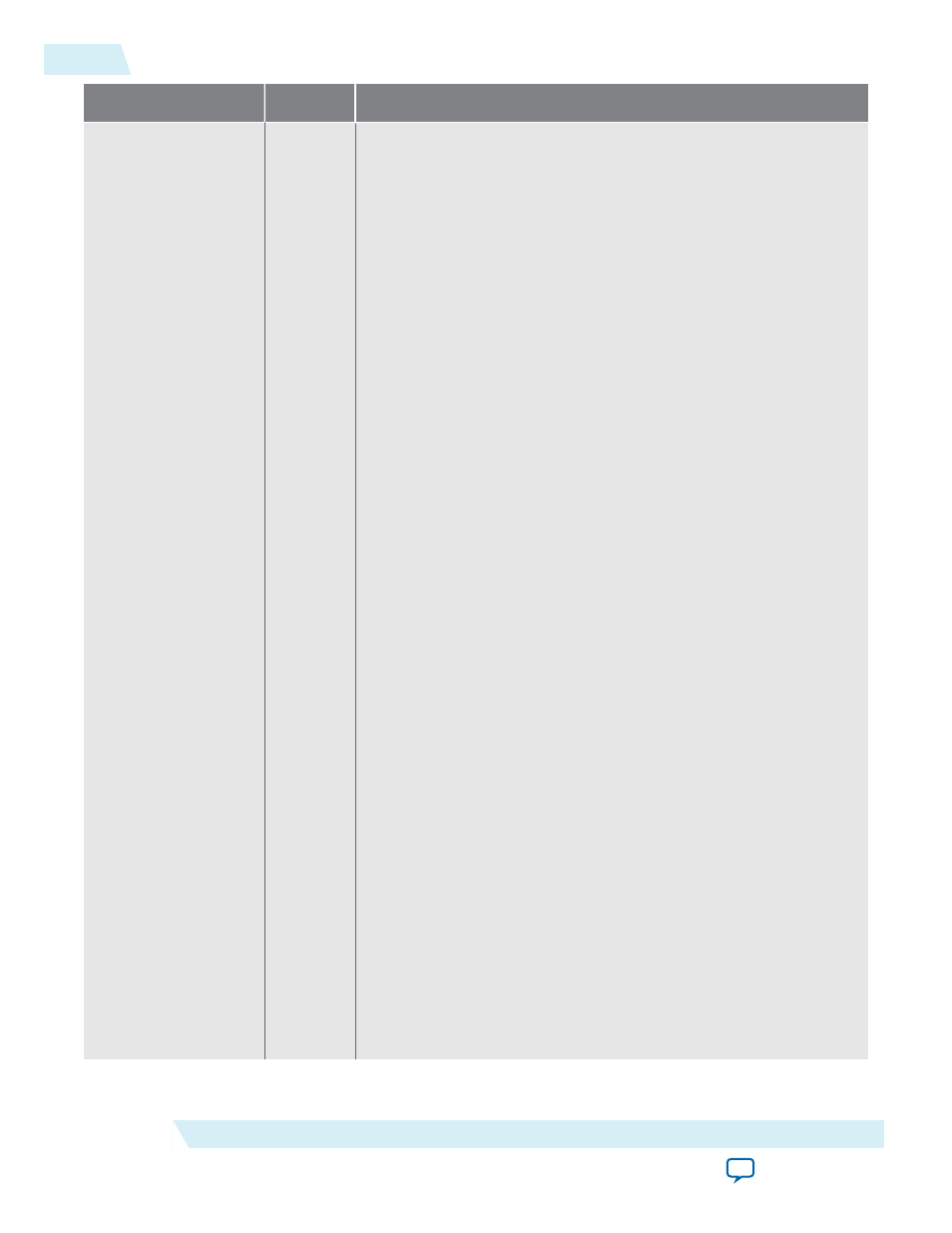

Date

Version

Changes Made

2014.06.30

14.0

Added the following new features to the Stratix V Hard IP for PCI

Express:

• Added parameters to enable 256 completion tags with completion

tag checking performed in Application Layer.

• Added simulation log file,

altpcie_monitor_sv_dlhip_tlp_file_log.log

,

that is automatically generated in your simulation directory. To

simulation in the Quartus II 14.0 software release, you must

regenerate your IP core to create the supporting monitor file the

generates

altpcie_monitor_sv_dlhip_tlp_file_log.log

. Refer to

Understanding Simulation Dump File Generation for details.

• Added support for new parameter,User ID register from the

Vendor Sepcific Extended Capability, for Endpoints.

• Added parameter to create a reset pulse at power-up when the soft

reset controller is enabled.

• Simulation support for Phase 2 and Phase 3 equalization when

requested by third-party BFM.

• Increased size of

lmi_addr

to 15 bits.

Made the following changes to the user guide:

• Added Next Steps in Creating a Design for PCI Express to

Datasheet chapter.

• Corrected frequency range for

hip_reconfig_clk

. It should be

100-125 MHz.

• Corrected Maximum payload size values listed in Reconfigurable

Read-Only Registers table. The maximum size is 2048 bytes.

• Enhanced definition of Device ID and Sub-system Vendor ID to

say that these registers are only valid in the Type 0 (Endpoint)

Configuration Space.

• Changed the default reset controller settings. By default Gen1

devices use the Hard Reset Controller. Gen2 and Gen3 devices use

the Soft Reset Controller.

• Corrected frequencies of

pclk

in Reset and Clocks chapter.

• Removed

txdatavalid0

signal from the PIPE interface. This

signal is not available.

• Removed references to the MegaWizard

®

Plug-In Manager. In

14.0 the IP Parameter Editor Powered by Qsys has replaced the

MegaWizard Plug-In Manager.

• Made the following changes to the timing diagram, Hard IP

Reconfiguration Bus Timing of Read-Only Registers:

• Added

hip_reconfig_rst_n

.

• Changed timing of

avmm_rdata[15:0]

. Valid data returns 4

cycles after

avmm_rd

.

C-2

Revision History for the Avalon-St Interface

UG-01097_avst

2014.12.15

Altera Corporation

Additional Information