Altera Stratix V Avalon-ST User Manual

Page 226

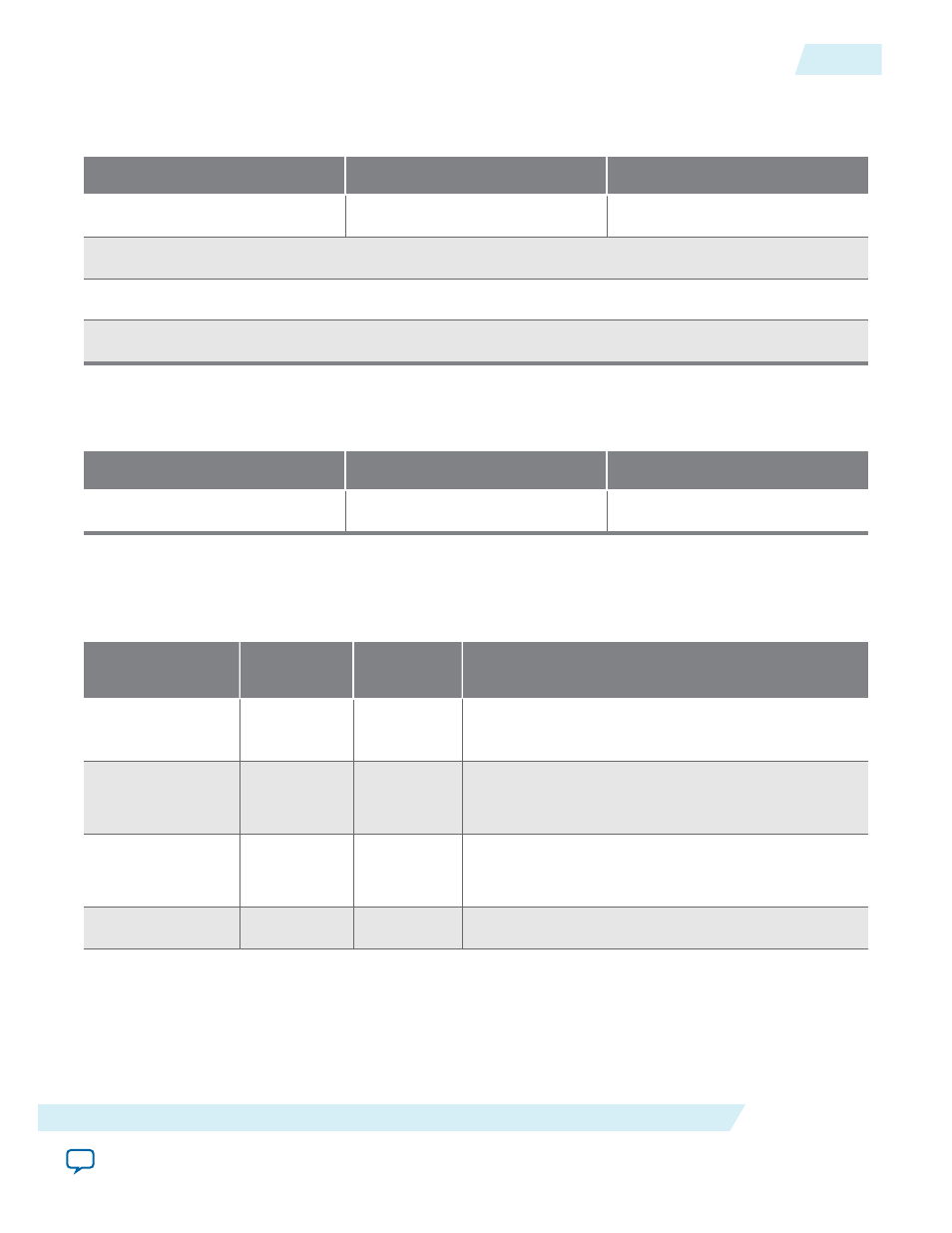

The following table shows the layout of the descriptor fields following the descriptor header.

Table 17-8: Chaining DMA Descriptor Format Map

Bits[31:22]

Bits[21:16]

Bits[15:0]

Reserved

Control Fields (refer to Table 18–9) DMA Length

Endpoint Address

RC Address Upper DWORD

RC Address Lower DWORD

The following table shows the layout of the control fields of the chaining DMA descriptor.

Table 17-9: Chaining DMA Descriptor Format Map (Control Fields)

Bits[21:18]

Bit[17]

Bit[16]

Reserved

EPLAST_ENA

MSI

Each descriptor provides the hardware information on one DMA transfer. The following table describes

each descriptor field.

Table 17-10: Chaining DMA Descriptor Fields

Descriptor Field

Endpoint

Access

RC Access

Description

Endpoint

Address

R

R/W

A 32-bit field that specifies the base address of the

memory transfer on the Endpoint site.

RC Address

Upper DWORD

R

R/W

Specifies the upper base address of the memory

transfer on the RC site.

RC Address

Lower DWORD

R

R/W

Specifies the lower base address of the memory

transfer on the RC site.

DMA Length

R

R/W

Specifies the number of DMA DWORDs to transfer.

UG-01097_avst

2014.12.15

Chaining DMA Descriptor Tables

17-15

Testbench and Design Example

Altera Corporation