Altera Stratix V Avalon-ST User Manual

Page 126

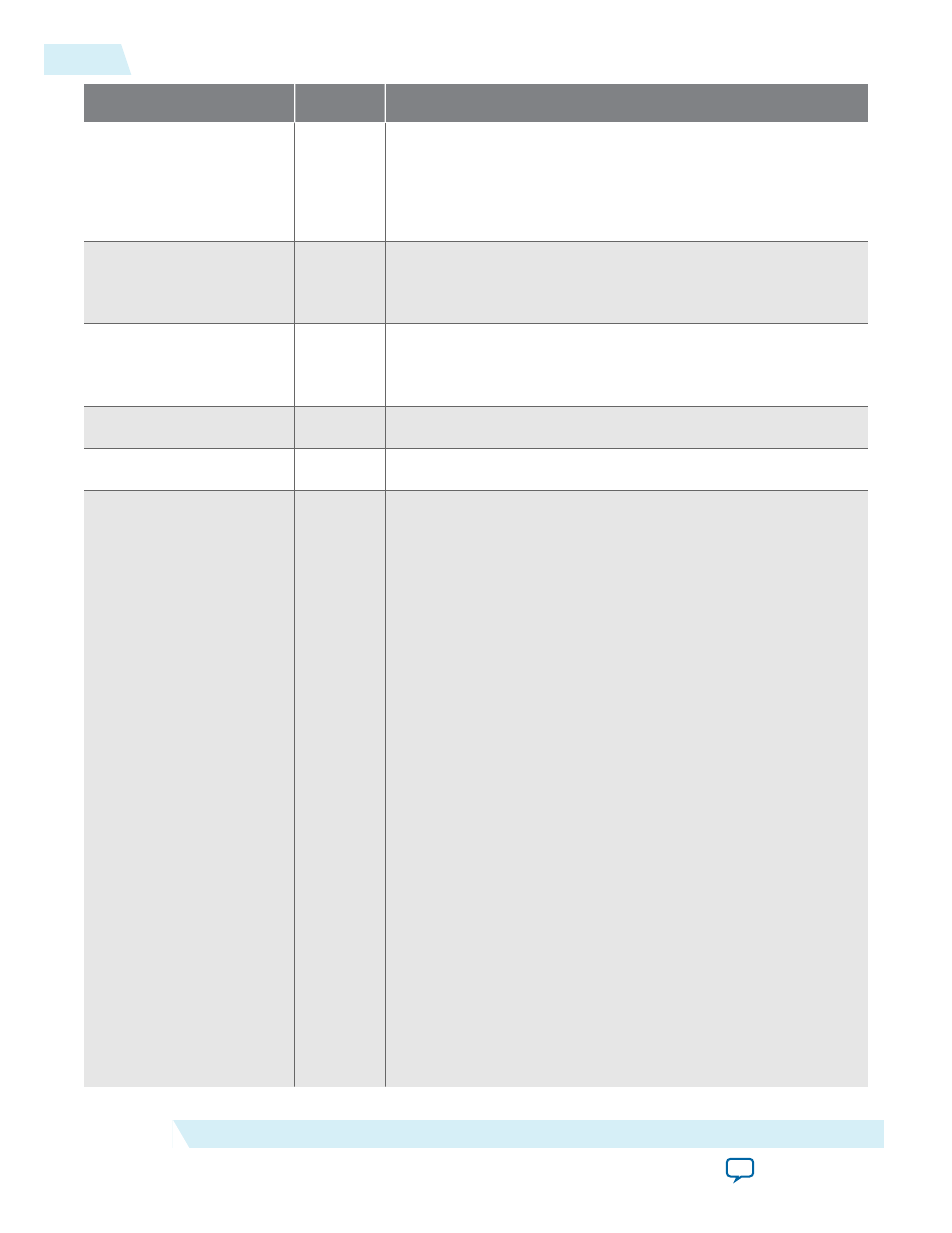

Signal

Direction

Description

sim_pipe_rate[1:0]

Output

The 2-bit encodings have the following meanings:

• 2’b00: Gen1 rate (2.5 Gbps)

• 2’b01: Gen2 rate (5.0 Gbps)

• 2’b1X: Gen3 rate (8.0 Gbps)

sim_pipe_pclk_in

Input

This clock is used for PIPE simulation only, and is derived from

the

refclk

. It is the PIPE interface clock used for PIPE mode

simulation.

sim_pipe_pclk_out

Output

TX datapath clock to the BFM PHY.

pclk_out

is derived from

refclk and provides the source synchronous clock for TX data

from the PHY.

sim_pipe_clk250_out

Output

Used to generate

pclk

.

sim_pipe_clk500_out

Output

Used to generate

pclk

.

sim_pipe_

ltssmstate0[4:0]

Input and

Output

LTSSM state: The LTSSM state machine encoding defines the

following states:

• 5’b00000: Detect.Quiet

• 5’b 00001: Detect.Active

• 5’b00010: Polling.Active

• 5’b 00011: Polling.Compliance

• 5’b 00100: Polling.Configuration

• 5’b00101: Polling.Speed

• 5’b00110: config.LinkwidthsStart

• 5’b 00111: Config.Linkaccept

• 5’b 01000: Config.Lanenumaccept

• 5’b01001: Config.Lanenumwait

• 5’b01010: Config.Complete

• 5’b 01011: Config.Idle

• 5’b01100: Recovery.Rcvlock

• 5’b01101: Recovery.Rcvconfig

• 5’b01110: Recovery.Idle

• 5’b 01111: L0

• 5’b10000: Disable

• 5’b10001: Loopback.Entry

• 5’b10010: Loopback.Active

• 5’b10011: Loopback.Exit

• 5’b10100: Hot.Reset

• 5’b10101: L0s

• 5’b11001: L2.transmit.Wake

5-74

PIPE Interface Signals

UG-01097_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions