Altera Stratix V Avalon-ST User Manual

Page 68

Single packer per cycle mode requires simpler Application Layer packet decode logic on the TX and RX

paths because packets always start in the lower 128-bits of the Avalon-ST interface. However, the Applica‐

tion Layer must still track Completion Credits to avoid RX buffer overflow. To track Completion Credits,

use the following signals to monitor the completion space available and to ensure enough space is

available before transmitting Non-Posted requests.

•

ko_cpl_spc_header

•

ko_cpl_spc_data

Data Alignment and Timing for 256‑Bit Avalon‑ST RX Interface

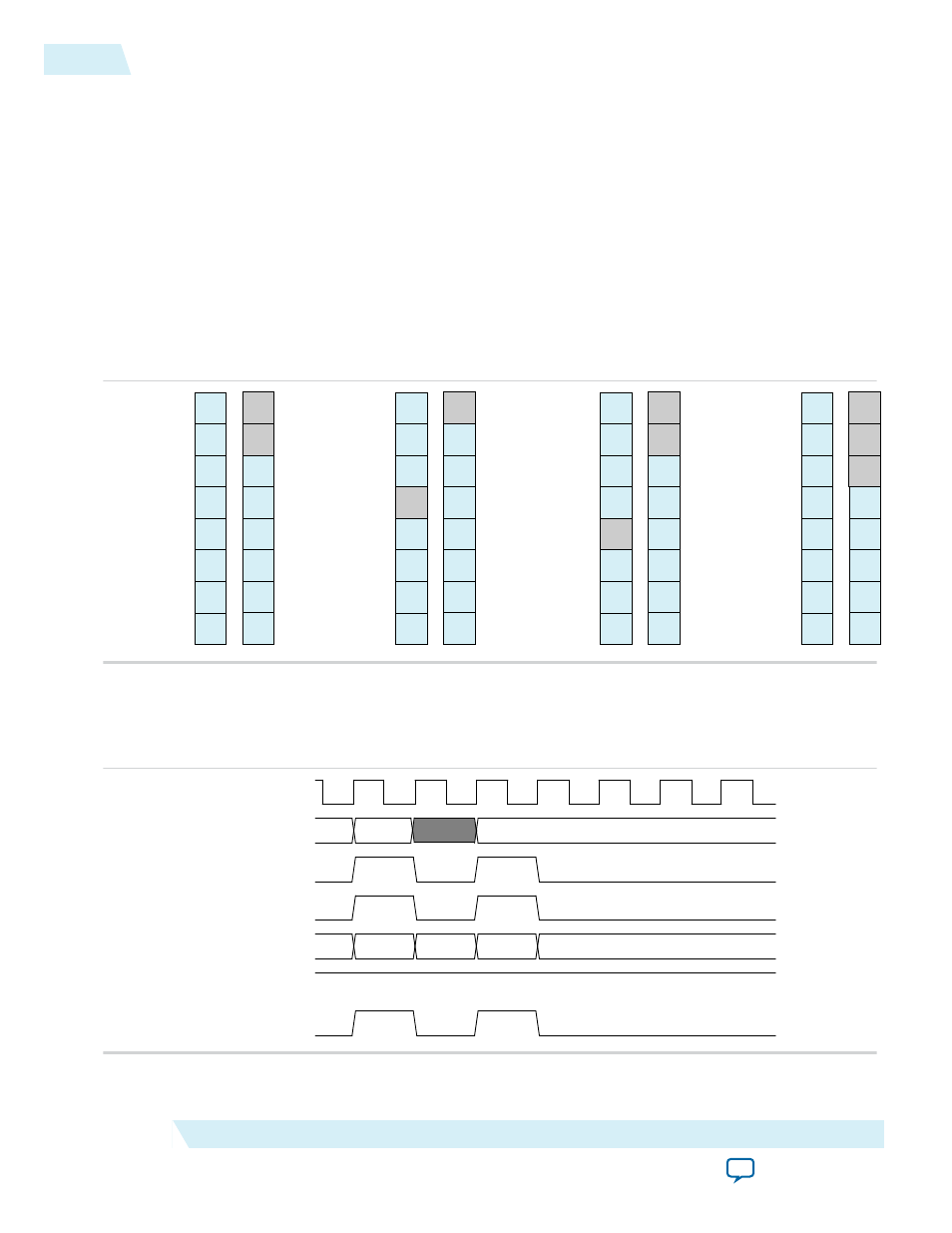

Figure 5-16: Location of Headers and Data for Avalon-ST 256-Bit Interface

The following figure shows the location of headers and data for the 256-bit Avalon-ST packets. This

layout of data applies to both the TX and RX buses.

D3

255

0

255

0

255

0

255

0

4DW header,

Aligned data

D2

D1

D0

H3

H2

H1

H0

D9

D8

D7

D6

D5

D4

D2

4DW header,

Unaligned data

D1

D0

H3

H2

H1

H0

D9

D8

D7

D6

D5

D4

D3

D3

3DW header,

Aligned data

D2

D1

D0

H2

H1

H0

D9

D8

D7

D6

D5

D4

D4

3DW header,

Unaligned data

D3

D2

D0

H2

H1

H0

D9

D8

D7

D6

D5

D1

Figure 5-17: 256-Bit Avalon-ST RX Packets Use of rx_st_empty and Single-Cycle Packets

The following figure illustrates two single-cycle 256-bit packets. The first packet has two empty qword,

rx_st_data[191:0]

is valid. The second packet has two empty dwords;

rx_st_data[127:0]

is valid.

pld_clk

rx_st_data[255:0]

rx_st_sop

rx_st_eop

rx_st_empty[1:0]

rx_st_ready

rx_st_valid

XX..BE ...

1

0

2

XXXXXXXXXXXXXXXX. . . 4592001487DF08876210...

5-16

Data Alignment and Timing for 256‑Bit Avalon‑ST RX Interface

UG-01097_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions