Pci express and pci capabilities parameters, Device capabilities – Altera Stratix V Avalon-ST User Manual

Page 45

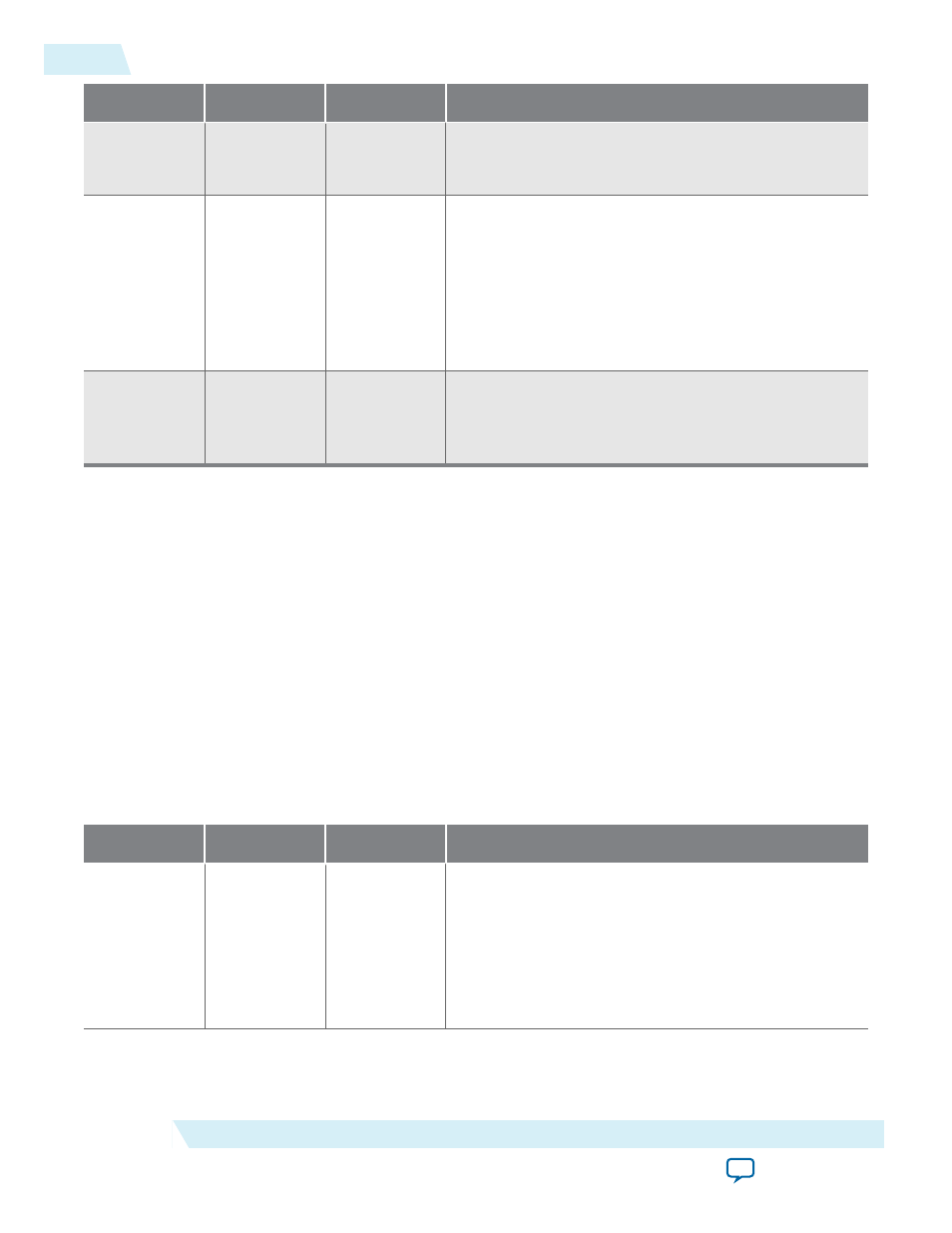

Register Name

Range

Default Value

Description

Class code

24 bits

0x00000000

Sets the read-only value of the

Class Code

register.

Address offset: 0x008.

Subsystem

Vendor ID

16 bits

0x00000000

Sets the read-only value of the

Subsystem Vendor ID

register in the PCI Type 0 Configuration Space. This

parameter cannot be set to 0xFFFF per the PCI Express

Base Specification. This value is assigned by PCI-SIG to

the device manufacturer. This register is only valid in

the Type 0 (Endpoint) Configuration Space.

Address offset: 0x02C.

Subsystem

Device ID

16 bits

0x00000000

Sets the read-only value of the

Subsystem Device ID

register in the PCI Type 0 Configuration Space.

Address offset: 0x02C

At run time, you can change the values of these registers using the optional reconfiguration block signals.

Related Information

•

on page 15-1

•

PCI Express and PCI Capabilities Parameters

This group of parameters defines various capability properties of the IP core. Some of these parameters

are stored in the PCI Configuration Space - PCI Compatible Configuration Space. The byte offset

indicates the parameter address.

Device Capabilities

Table 4-5: Capabilities Registers

Parameter

Possible Values

Default Value

Description

Maximum

payload size

128 bytes

256 bytes

512 bytes

1024 bytes

2048 bytes

128 bytes

Specifies the maximum payload size supported. This

parameter sets the read-only value of the max payload

size supported field of the Device Capabilities register

(0x084[2:0]). Address: 0x084.

4-8

PCI Express and PCI Capabilities Parameters

UG-01097_avst

2014.08.18

Altera Corporation

Parameter Settings