Configuration space register access timing, Configuration space register access – Altera Stratix V Avalon-ST User Manual

Page 108

Configuration Space Register Access Timing

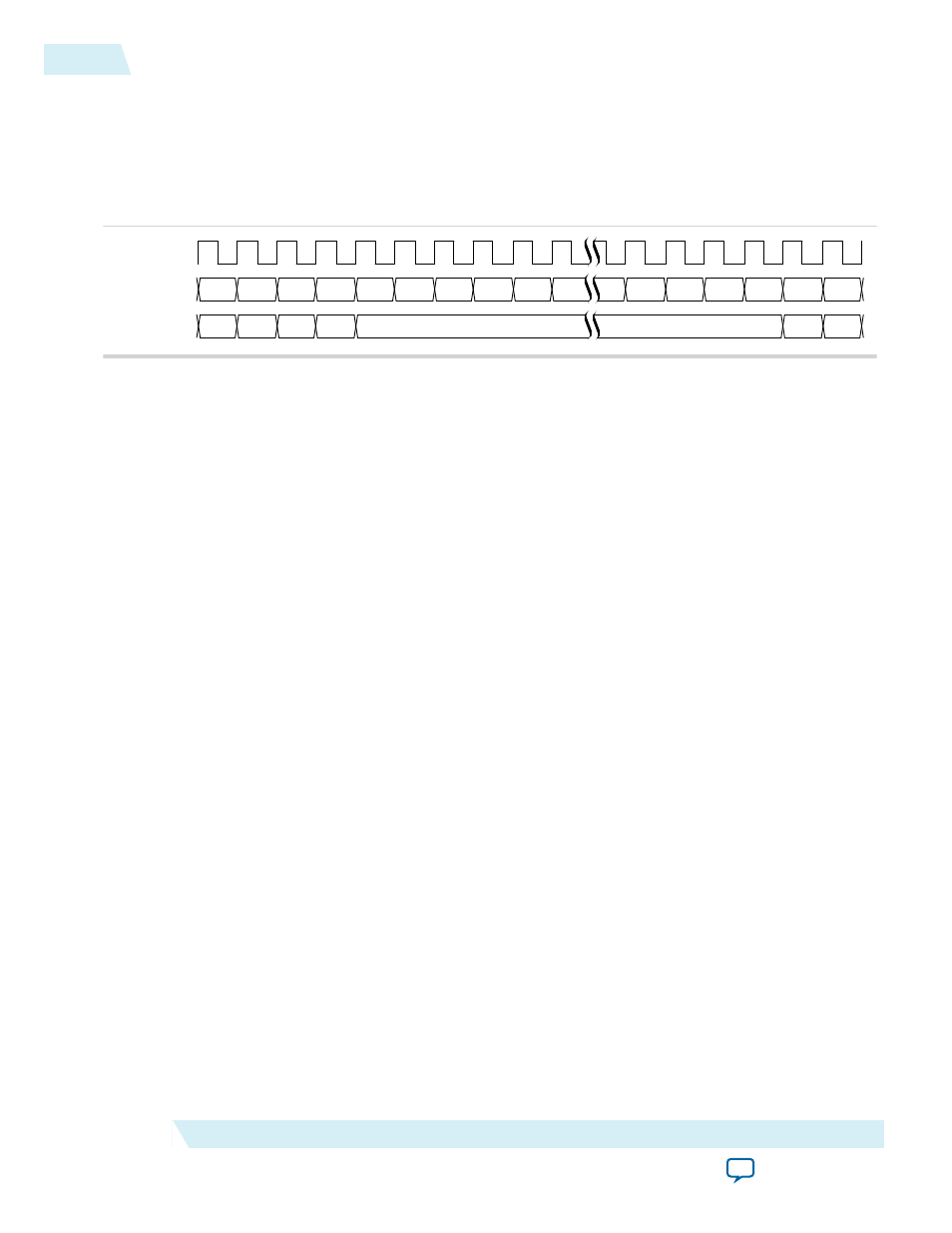

Figure 5-38: tl_cfg_ctl Timing

The following figure shows typical traffic on the

tl_cfg_ctl

bus. The

tl_cfg_add

index increments on

the rising edge of the

pld_clk

. The address specifies which Configuration Space register data value is

being driven onto

tl_cfg_ctl

.

pld_clk

tl_cfg_add[3:0]

tl_cfg_ctl[31:0]

2

3

4

5

6

7

8

9

A

B

8

9

A

B

C

D

E

00... 00... 00... 7F...

00000000

00000000

00... 00...

Configuration Space Register Access

The

tl_cfg_ctl

signal is a multiplexed bus that contains the contents of Configuration Space registers as

shown in the figure below. Information stored in the Configuration Space is accessed in round robin

order where

tl_cfg_add

indicates which register is being accessed. The following table shows the layout

of configuration information that is multiplexed on

tl_cfg_ctl

.

5-56

Configuration Space Register Access Timing

UG-01097_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions