Altera Stratix V Avalon-ST User Manual

Page 97

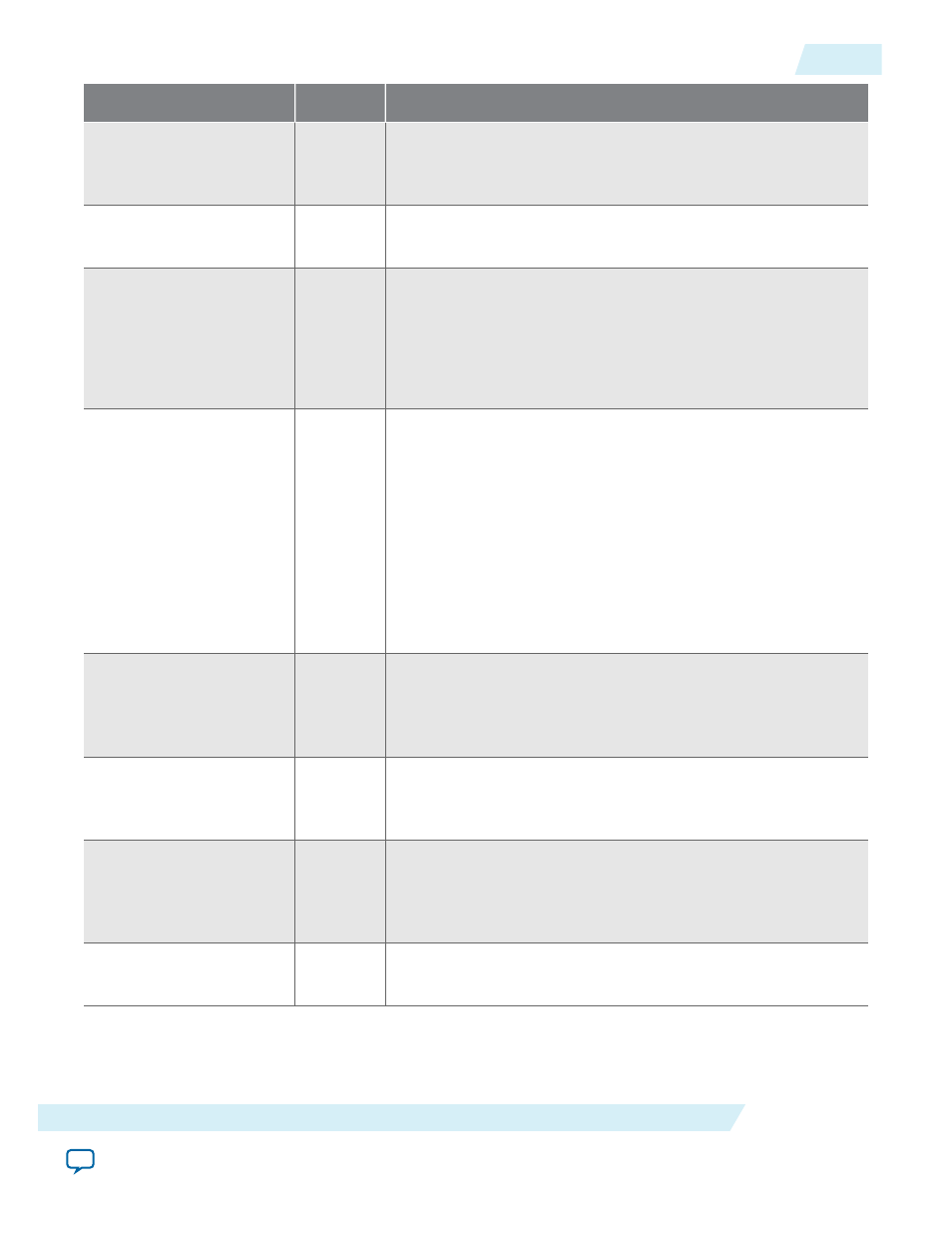

Signal Name

Direction

Description

tx_req_pm

Input

Assert this signal to request that the TX Data Link Layer send a

Power Management Data Link Layer Packet of type

tx_typ_pm_

pld

. Deasserts when

tx_ack_pm_pld

is asserted.

tx_typ_pm[2:0]

Input

Lowest 3 bits of the type field for the Power Management Data

Link Layer Packet being requested by

tx_req_pm_pld

.

req_phypm[3:0]

Input

Directs the LTSSM to low power mode.

•

req_phypm[3]

: L2 request

•

req_phypm[2]

: L1 request

•

req_phypm[1]

: L0s request

•

req_phypm[0]

: exit any low power state to L0

req_phycfg[3:0]

Input

Configuration Space transition request bus:

•

req_phycfg[3]

: Link retrain request. Retrain the link by

writing 1b’1 in the retrain link bit in the

Link Control

Register

.

•

req_phycfg[2]

: Recovery link request. Directs the LTSSM to

the Recovery state.

•

req_phycfg[1]

: Hot Reset request. Directs the LTSSM to the

Hot Reset state.

•

req_phycfg[0]

: Disable Link request. Directs the LTSSM to

the Disable state.

vc0_tcmap_pld[7:1]

Input

Each bit corresponds to a Traffic Class. Bits[7:1] correspond to

Traffic Class 7–Traffic Class 1. When a bit is set to 1, indicates

that the corresponding Traffic Class maps to VC0. Traffic Class 0

always maps to Virtual Channel 0.

inh_dllp

Input

When asserted, all TLP and DLLP transmission requests are

stalled at the TX Data Link to PHY interface, except for NAK and

Power Management DLLPs.

inh_tx_tlp

Input

When asserted, all TLP transmission requests are stalled at the

TX Transaction Layer to Data Link Layer interface. The Applica‐

tion Layer should assert this signal when requesting a low-power

state.

req_wake

Input

When asserted, requests the LTSSM to exit from a low-power

state.

UG-01097_avst

2014.12.15

Configuration Space Bypass Mode Interface Signals

5-45

Interfaces and Signal Descriptions

Altera Corporation