Cpu interface signals, Cpu interface signals –11 – Altera CPRI IP Core User Manual

Page 109

Chapter 6: Signals

6–11

CPU Interface Signals

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

CPU Interface Signals

Table 6–8

lists the CPU interface signals. The CPU interface is implemented as an

Avalon-MM interface.

f

for details about the Avalon-MM interface.

cpri_mii_txd[3:0]

Input

Ethernet transmit nibble data. The data transmitted from the external Ethernet block to

the CPRI IP core, for transmission on the CPRI link. This input bus is synchronous to

the rising edge of the

cpri_clkout

clock.

cpri_mii_txrd

Output

Ethernet read request. Indicates that the MII block is ready to read data on

cpri_mii_txd[3:0]

. Valid data is recognized 2

cpri_mii_txclk

cycles after

cpri_mii_txen

is asserted in response to

cpri_mii_txrd

. The

cpri_mii_txrd

signal remains asserted for 2

cpri_mii_txclk

cycles following deassertion of

cpri_mii_txen

. Deasserting

cpri_mii_txrd

while

cpri_mii_txen

is still

asserted backpressures the external Ethernet block.

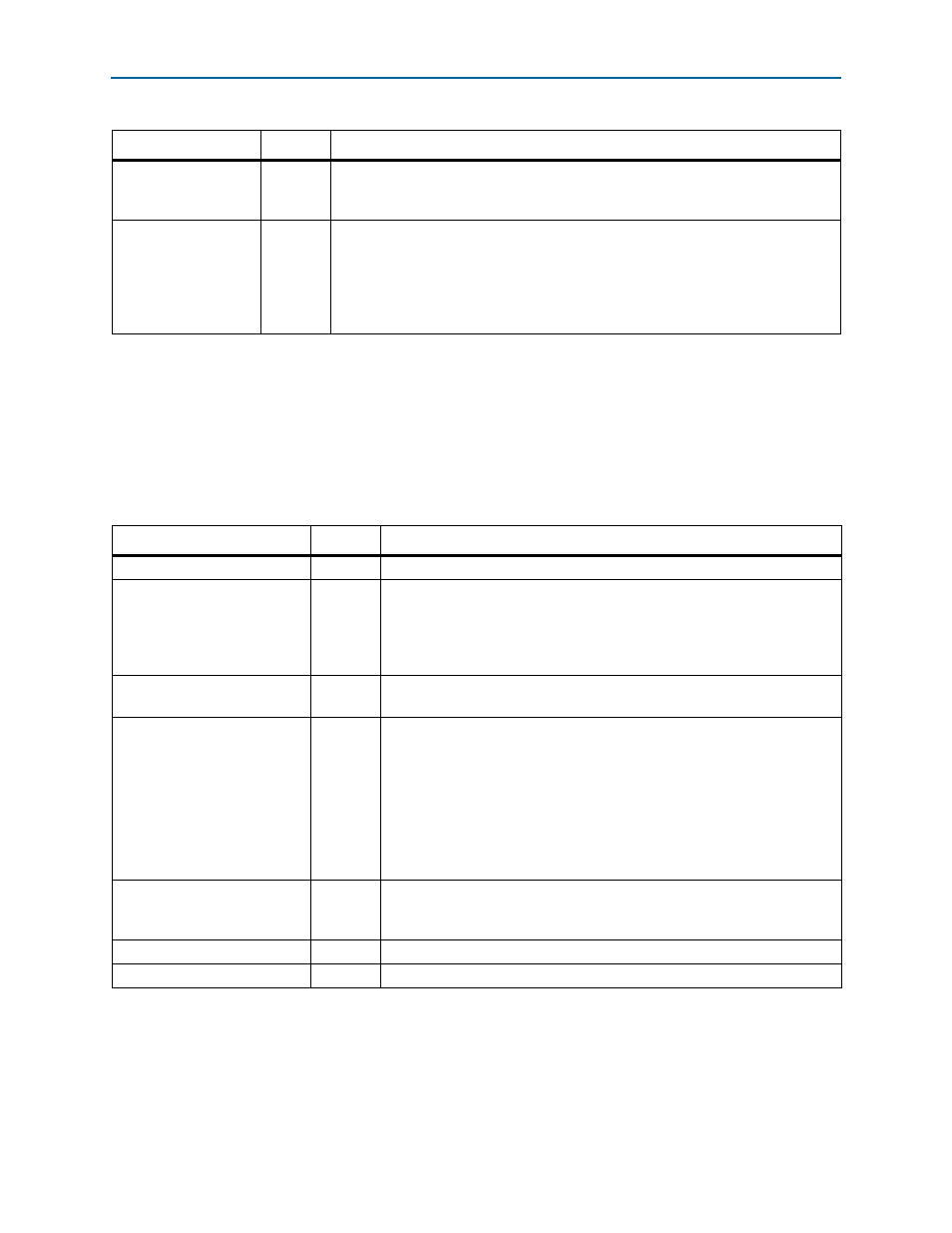

Table 6–7. CPRI MII Transmitter Interface Signals (Part 2 of 2)

Signal

Direction

Description

Table 6–8. CPU Interface Signals (Part 1 of 2)

Signal

Direction

Description

cpu_clk

Input

CPU clock signal.

cpu_reset

Input

CPU peripheral reset. This reset is associated with the

cpu_clk

clock.

cpu_reset

can be asserted asynchronously, but must stay asserted at least

one

cpu_clk

cycle and must be de-asserted synchronously with

cpu_clk

.

for a circuit that shows how to enforce

synchronous deassertion of a reset signal.

cpu_irq

Output

Merged CPU interrupt indicator. This signal is the

OR

of all the bits in the

vector

cpu_irq_vector

.

cpu_irq_vector[4:0]

Output

This vector contains the following interrupt bits:

[0]

cpu_irq_cpri

: Interrupt bit from

CPRI_INTR

register. This signal is

the

OR

of all three interrupt bits in the CPRI_INTR register.

[1]

cpu_irq_eth_rx

: Interrupt from the Ethernet receiver module.

[2]

cpu_irq_eth_tx

: Interrupt from the Ethernet transmitter module.

[3]

cpu_irq_hdlc_rx

: Interrupt from the HDLC receiver module.

[4]

cpu_irq_hdlc_tx

: Interrupt from the HDLC transmitter module.

cpu_address[13:0]

Input

CPU word address. Corresponds to bits [15:2] of a byte address with LSBs

2’b00. If you connect an Avalon-MM interface to the CPU interface, connect

bits [15:2] of the incoming Avalon-MM address to

cpu_address

.

cpu_write

Input

CPU write request.

cpu_read

Input

CPU read request.