Altera CPRI IP Core User Manual

Page 216

Info–4

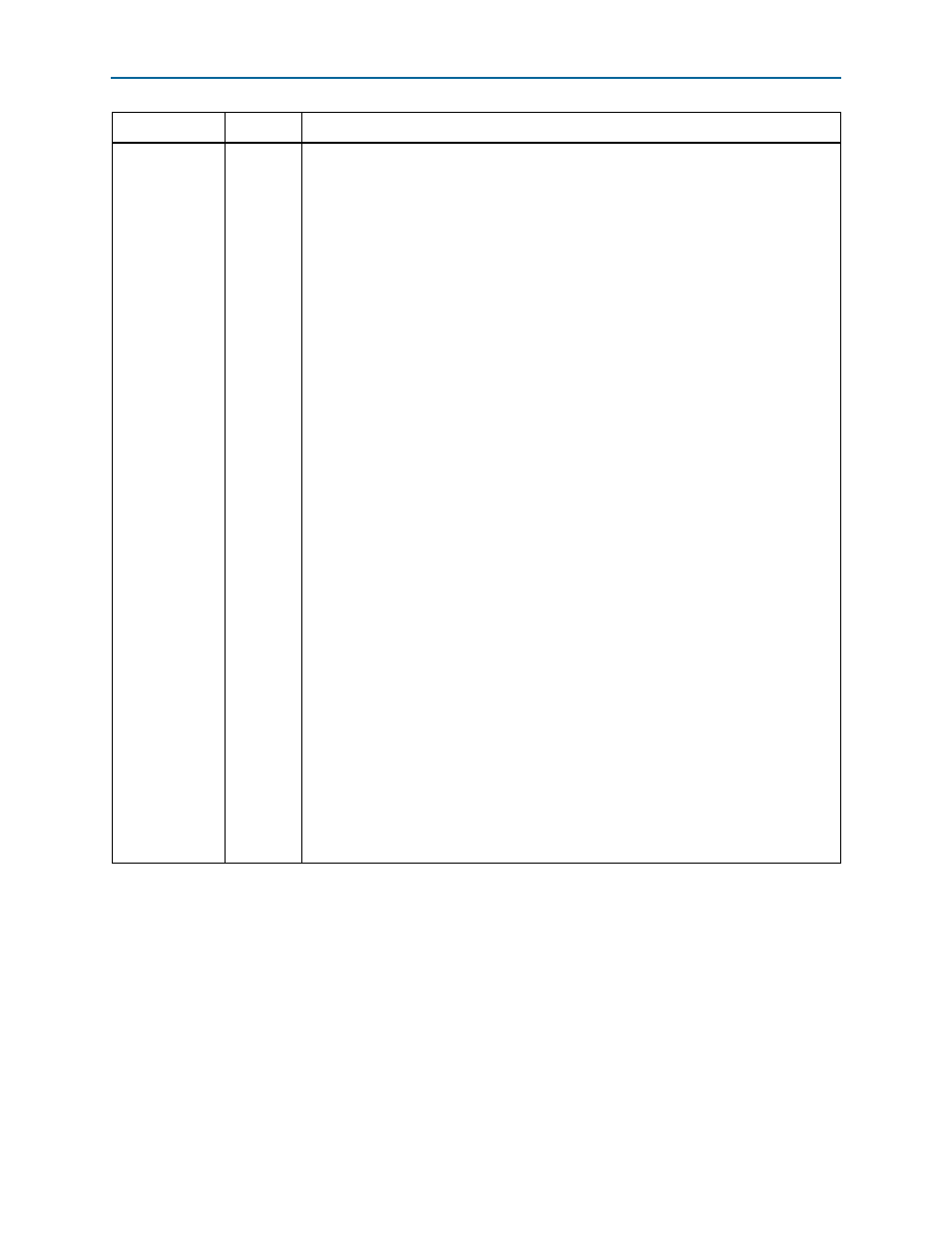

Additional InformationAdditional Information

Document Revision History

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

May 2012

12.0

■

Added CPRI line rate of 9.8 Gbps in Arria V GT and Stratix V devices.

■

Added support for autorate negotiation up to 6.144 Gbps in Arria V devices.

■

Added support for autorate negotiation up to 9.8 Gbps in Stratix V devices.

■

Added new parameter to specify inclusion or exclusion of an HDLC block.

■

Added new parameter to specify the MAP interface mapping mode.

■

Updated

Figure 4–27 on page 4–56

, CPRI Frame Synchronization Machine, to include

the descrambling conditions and remove a redundant state.

■

Updated

Figure 4–14 on page 4–27

and discussion of MAP interface TX synchronous

buffer mode to encourage the application to assert

mapN_tx_resync

and

mapN_tx_valid

simultaneously.

■

Updated clocks presentation in

“Clocking Structure” on page 4–3

and separated from

reset signals presentation.

■

Updated

Chapter 8, Testbenches

with new testbenches for Arria V and Stratix V devices.

■

Moved information about loopback modes and PRBS generation and testing from

Chapter 4, Functional Description

to new

Chapter 5, Testing Features

.

■

Moved information about the advanced AxC mapping modes from

Chapter 4, Functional

Description

to new appendix

Appendix C, Advanced AxC Mapping Modes

and updated

the presentation.

■

Moved information about the RX delay measurement and TX delay calibration from

Chapter 4, Functional Description

to new appendix

Appendix D, Delay Measurement and

Calibration

.

■

Added new appendix

Appendix E, Integrating the CPRI IP Core Timing Constraints in the

Full Design

.

■

Reordered sections in

Chapter 4, Functional Description

to emphasize the MAP and AUX

interfaces and to group together the modules accessed through the CPU interface.

■

Reordered presentation of signals in

Chapter 6, Signals

to reflect order in

Chapter 4,

Functional Description

.

■

Enhanced description of control word access through CPU interface in new section

“Accessing the Hyperframe Control Words” on page 4–42

.

■

Updated description of Ethernet communication through the CPU interface in

“Accessing the Ethernet Channel” on page 4–47

.

■

Moved

“Reset Control Word” on page 4–57

from Reset section of

“Reset

Requirements” on page 4–11

to

“CPRI Protocol Interface Layer (Physical Layer)” on

page 4–51

.

Date

Version

Changes Made