Operation mode parameter, Line rate parameter, Operation mode parameter –2 line rate parameter –2 – Altera CPRI IP Core User Manual

Page 26

3–2

Chapter 3: Parameter Settings

Physical Layer Parameters

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

Operation Mode Parameter

The Operation mode parameter specifies whether the CPRI IP core is configured with

slave clocking mode or with master clocking mode. An REC is configured with master

clocking mode.

The value of this parameter determines the initial operation mode of the CPRI IP core.

In IP core variations that target an Arria V, Cyclone V, or Stratix V device, you can

modify the IP core operation mode dynamically by modifying the value of the

operation_mode

bit of the

CPRI_CONFIG

register (

).

In your design, you must connect the clocks appropriately for the operation mode.

Refer to

“Clock Diagrams for the CPRI IP Core” on page 4–5

For information about how to dynamically switch the clock mode of your CPRI IP

core in variations that target an Arria V, Cyclone V, or Stratix V device, refer to

“Dynamically Switching Clock Mode” on page 4–9

Line Rate Parameter

The Line rate parameter specifies the line rate on the CPRI link in gigabits per second

(Gbps).

lists the CPRI line rates that each device family supports. A

checkmark indicates a supported variation.

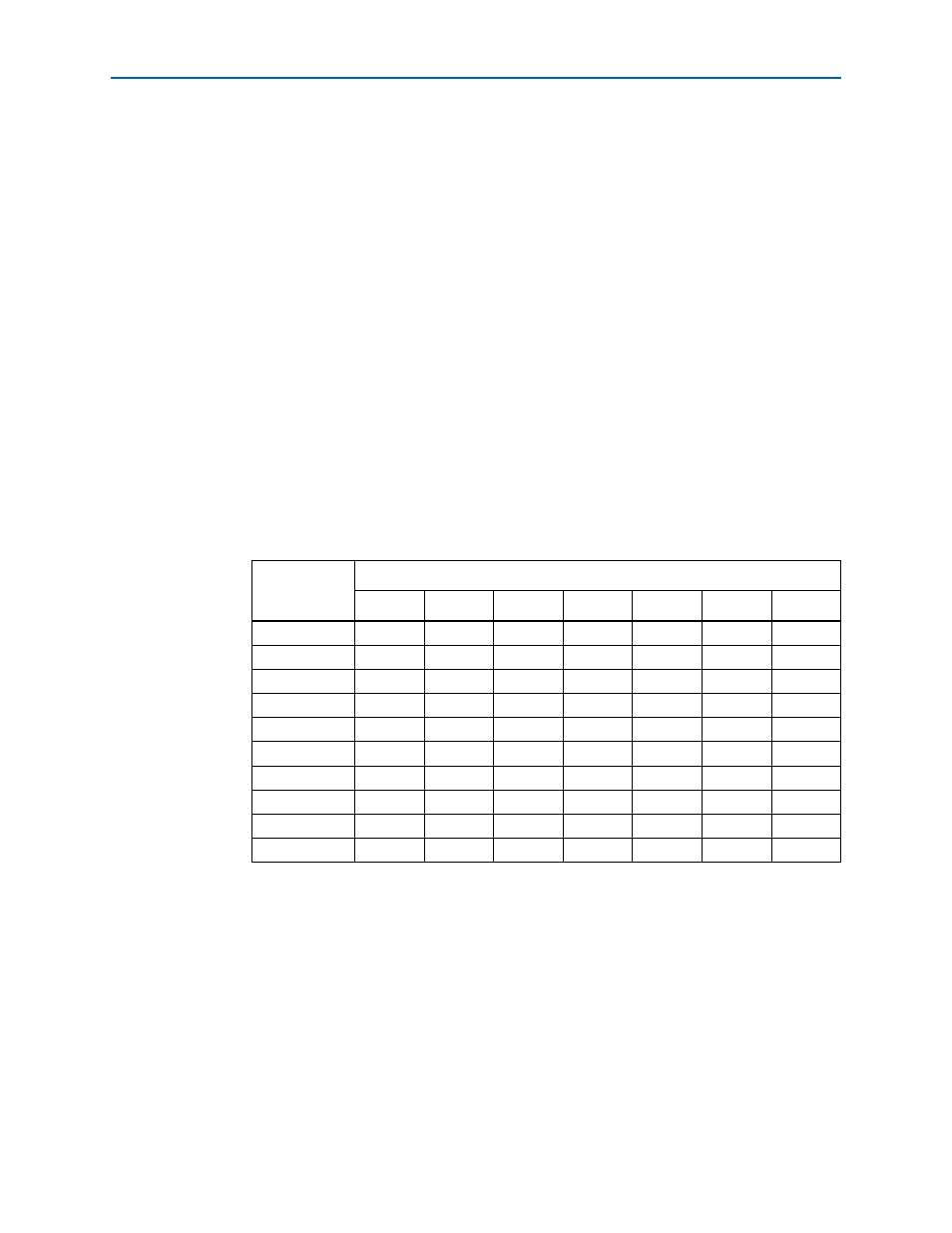

Table 3–1. Device Family Support for CPRI Line Rates

Device Family

or Variant

CPRI Line Rate (Gbps)

0.6144

1.2288

2.4576

3.072

4.9152

6.144

9.8304

Arria II GX

v

v

v

v

v

v

—

Arria II GZ

v

v

v

v

v

v

—

Arria V GX

v

v

v

v

v

v

—

Arria V GT

v

v

v

v

v

v

v

Arria V GZ

v

v

v

v

v

v

v

Cyclone IV GX

v

v

v

v

—

—

—

Cyclone V GX

v

v

v

v

—

—

—

Stratix IV GX

v

v

v

v

v

v

—

Stratix V GX

v

v

v

v

v

v

v

Stratix V GT

v

v

v

v

v

v

v

Note to

:

(1) Refer to

for information about the device speed grades that support each CPRI line rate.

The parameter editor does not enforce these restrictions. However, if you target a device whose speed grade does

not support the CPRI line rate you configure, compilation fails because the design cannot meet timing in hardware.